Ttl i/os, Leds, Jtag – Sundance SMT351 User Manual

Page 10: Switch, Table 1: led description

Version 1.6

Page 10 of 25

SMT351 User Manual

TTL I/Os.

Four TTL I/Os supporting LVTTL signals are connected directly to the FPGA (JP2).

These I/Os are not used by Sundance firmware and are available for customer use.

You must ensure that any lines you connect to these pins are LVTTL compatible in

order to protect the FPGA pads, as lines are not clamped.

section for more details.

LEDs

Five LEDs are available on the board. They are all driven by the FPGA.

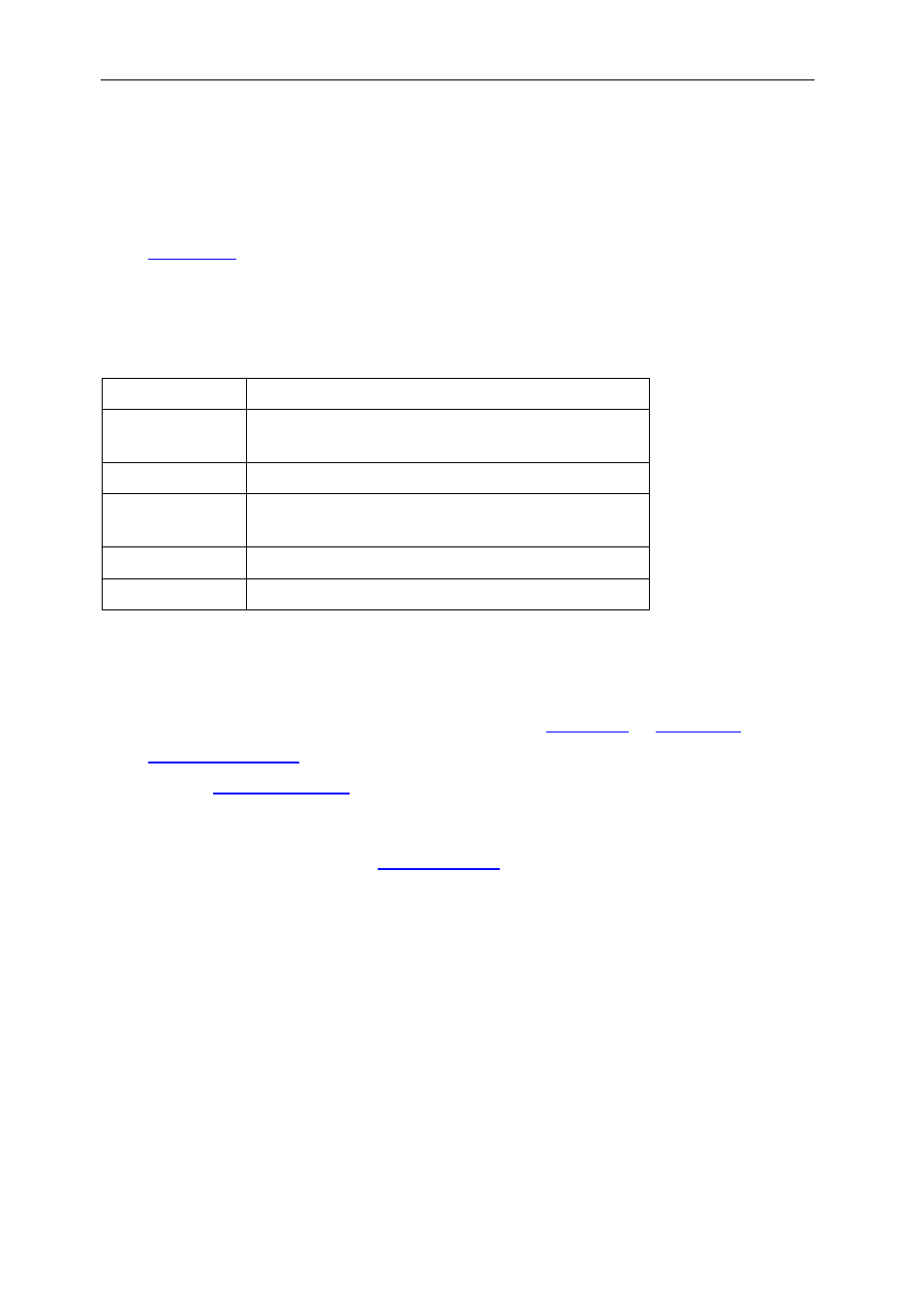

Table 1: LED description

LED #

Description

D1

FPGA Done pin. The LED is on when FPAG is

NOT configured.

D2 Unused.

D3

Image of DDR SDRAM clock (board “heart

beat”).

D4 Unused.

D5 Unused.

JTAG

The SMT351 includes a 6-pin JTAG header (2mm DIL header), which allows re-

programming the FPGA using a cable such as Xilinx

section for its location on board.

Refer to the

for the pinout of this connector.

Switch

SMT351 provides two switches:

SW1 is connected to CPLD and SW2 is connected to FPGA. SW2 is unused by the

default firmware.