Control register – Sensoray 518 User Manual

Page 13

12

Control Register

The control register provides the means for host management of interrupts and coprocessor soft

reset.

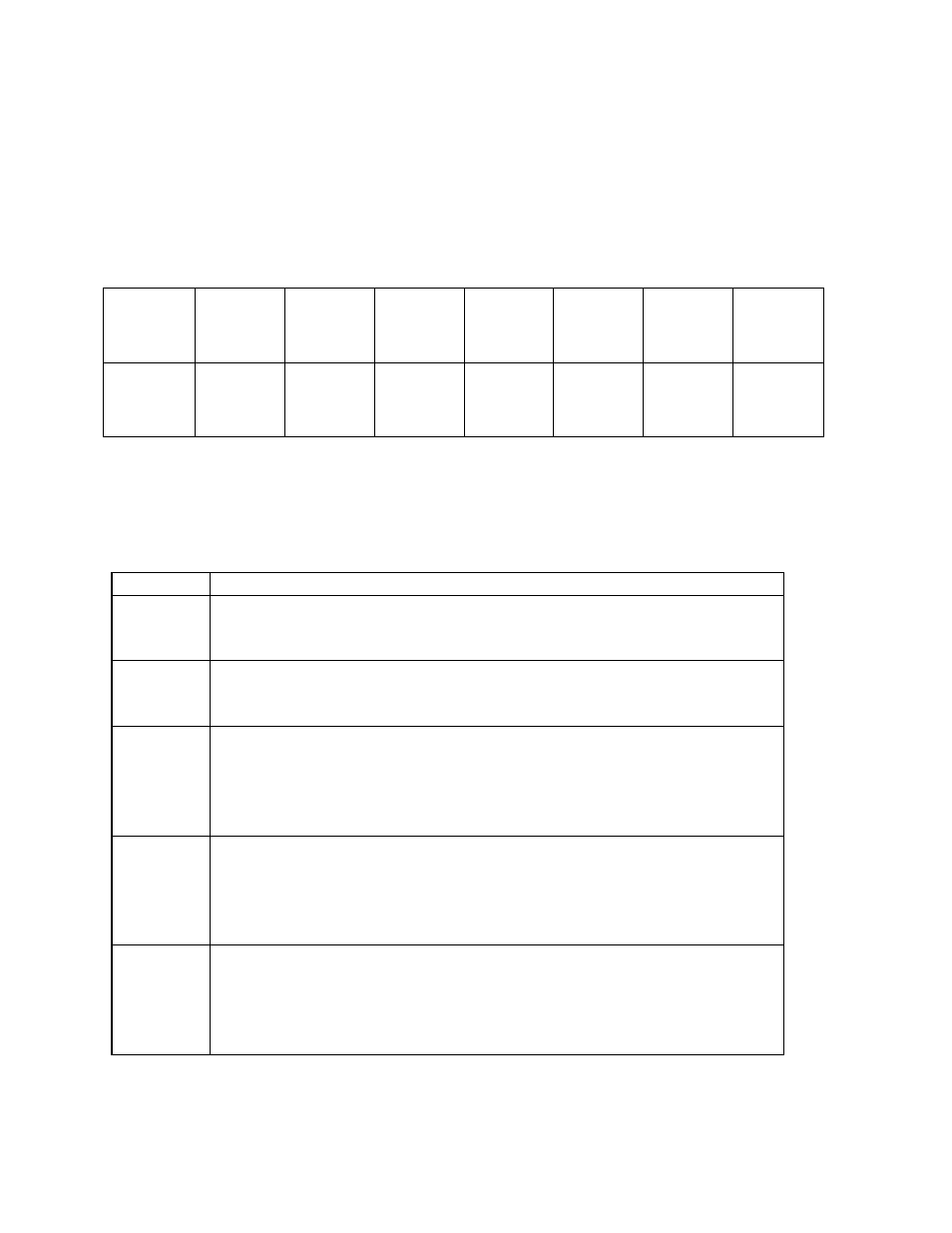

D7

D6

D5

D4

D3

D2

D1

D0

SET/CLR

0

0

INT/RST

0

ICMD

IDAT

IALARM

Control register bits have the following functions:

Name

Function

INT/

RST

Specifies the control function to be performed. When set to logic zero, the

518 board is reset and all other control register bits are ignored. When set

to logic one, the other control register bits behave as described below.

SET/

CLR

Specifies whether selected interrupts are to be enabled or disabled. When

set to logic one, all selected interrupts are enabled. When set to logic zero,

selected interrupts are disabled.

ICMD

Selects CRMT interrupt. When set to logic one, the CRMT interrupt is

enabled or disabled as determined by the state of the SET/CLR bit. When

set to logic zero, the CRMT interrupt enable is unchanged. While

enabled, the host will be interrupted whenever the status register CRMT

bit is asserted.

IDAT

Selects DAV interrupt. When set to logic one, the DAV interrupt is

enabled or disabled as determined by the state of the SET/CLR bit. When

set to logic zero, the DAV interrupt enable is unchanged. While enabled,

the host will be interrupted whenever the status register DAV bit is

asserted.

IALARM

Selects ALARM interrupt. When set to logic one, the ALARM interrupt

is enabled or disabled as determined by the state of the SET/CLR bit.

When set to logic zero, the ALARM interrupt enable is unchanged. While

enabled, the host will be interrupted whenever the status register ALARM

bit is asserted.