Accuracy, Analog input drift, Noise performance – Measurement Computing PCIe-DAS1602/16 User Manual

Page 17

PCIe-DAS1602/16 User's Guide

Specifications

17

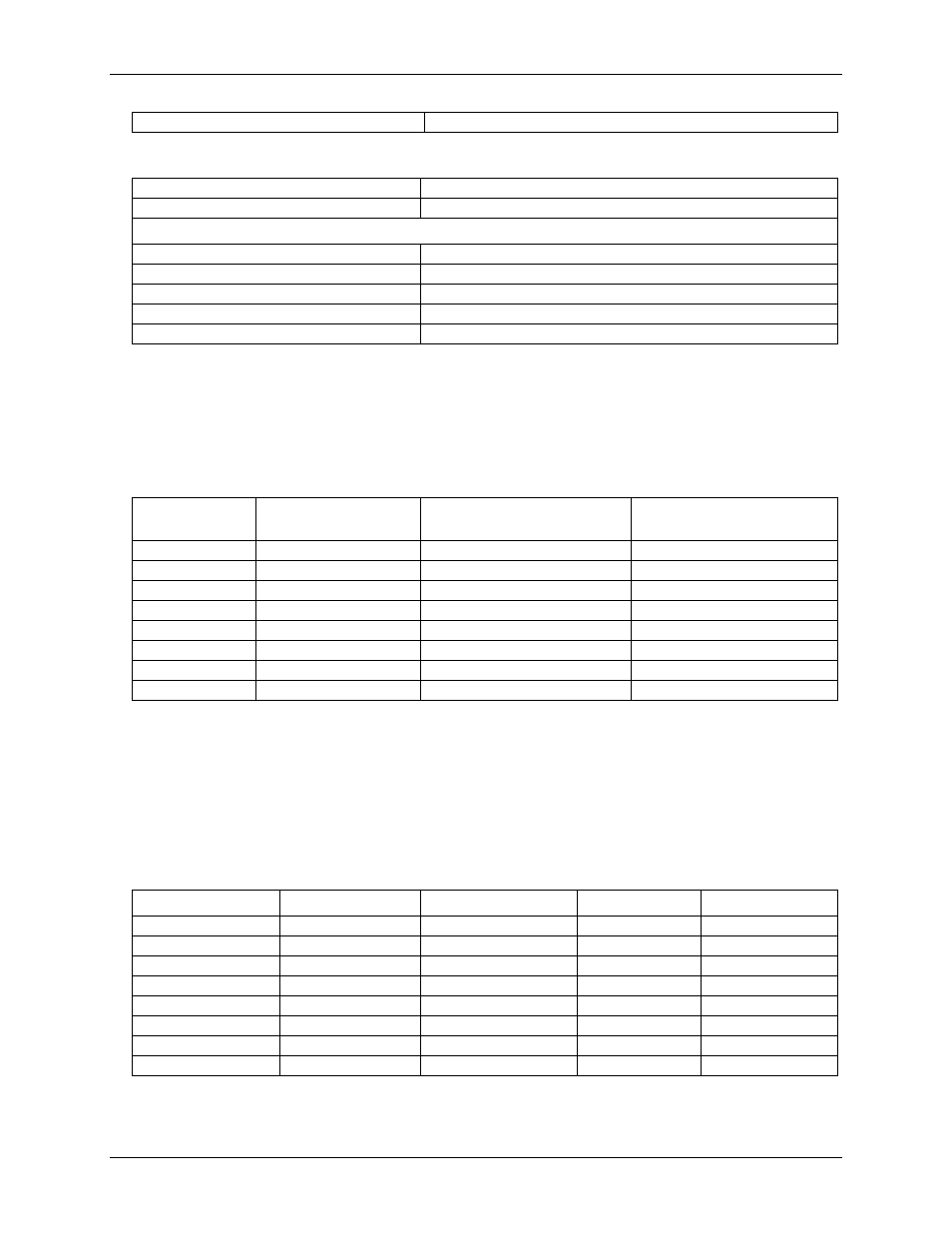

Absolute maximum input voltage

55 V/–40 V fault protected via input mux

Accuracy

Typical accuracy

±2.3 LSB

Absolute accuracy

±5.0 LSB

Accuracy Components

Gain error

Trimmable by potentiometer to 0

Offset error

Trimmable by potentiometer to 0

PGA linearity error

±1.3 LSB typ , ±10.0 LSB max

Integral linearity error

±0.5 LSB typ , ±3.0 LSB max

Differential linearity error

±0.5 LSB typ, ±2.0 LSB max

Each PCIe-DAS1602/16 is tested at the factory to assure the overall error of the board does not exceed ±5 LSB.

Total board error is a combination of gain, offset, differential linearity, and integral linearity error. The

theoretical absolute accuracy of the board may be calculated by summing these component errors. Worst case

error is realized only in the unlikely event that each of the component errors is at their maximum level, and

causes error in the same direction.

Analog input drift

Range

Analog Input FS Gain

Drift

Analog Input Zero drift

Overall Analog Input Drift

±10.00 V

2.2 LSB/°C max

1.8 LSB/°C max

4.0 LSB/°C max

±5.000 V

2.2 LSB/°C max

1.9 LSB/°C max

4.1 LSB/°C max

±2.500 V

2.2 LSB/°C max

2.0 LSB/°C max

4.2 LSB/°C max

±1.250 V

2.2 LSB/°C max

2.3 LSB/°C max

4.5 LSB/°C max

0 V to 10.00 V

4.1 LSB/°C max

1.9 LSB/°C max

6.0 LSB/°C max

0 V to 5.000 V

4.1 LSB/°C max

2.1 LSB/°C max

6.2 LSB/°C max

0 V to 2.500 V

4.1 LSB/°C max

2.4 LSB/°C max

6.5 LSB/°C max

0 V to 1.250 V

4.1 LSB/°C max

3.0 LSB/°C max

7.1 LSB/°C max

Absolute error change per °C temperature change is a combination of the gain and offset drift of many

components. The theoretical worst case error of the board may be calculated by summing these component

errors. Worst case error is realized only in the unlikely event that each of the component errors is at their

maximum level, and causes error in the same direction.

Noise performance

The following table summarizes the worst case noise performance for the PCIe-DAS1602/16. Noise distribution

is determined by gathering 50,000 samples with inputs tied to ground at the PCIe-DAS1602/16 main connector.

Data is for both SE and DIFF modes of operation.

Range

±2 counts

±1 count

Max Counts

LSBrms (Note 1)

±10.00 V

97%

80%

11

1.7

±5.000 V

97%

80%

11

1.7

±2.500 V

96%

79%

11

1.7

±1.250 V

96%

79%

11

1.7

0 V to 10.000 V

88%

65%

15

2.3

0 V to 5.000 V

88%

65%

15

2.3

0 V to 2.500 V

83%

61%

15

2.3

0 V to 1.250 V

83%

61%

16

2.4

Note 1:

Input noise is assumed to be Gaussian. An RMS noise value from a Gaussian distribution is calculated

by dividing the peak-to-peak bin spread by 6.6.