Controls, leds, and connectors – Artesyn COMX-P2020 Installation and Use (February 2015) User Manual

Page 57

Controls, LEDs, and Connectors

COMX-P2020 Module Installation and Use (6806800K97E)

57

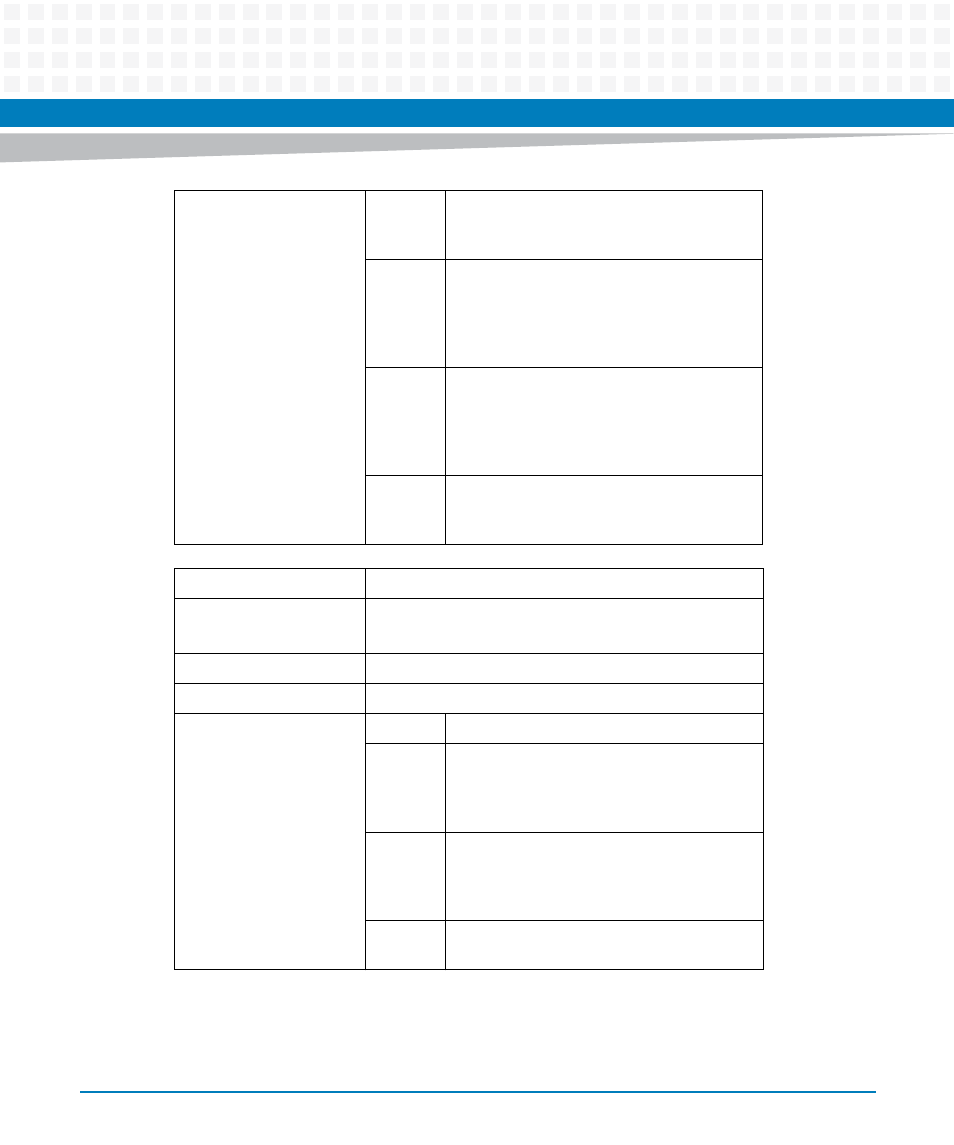

Supported configuration

00

CPU boot holdoff mode for both cores. The

cores are prevented from booting until

configured by an external master.

01

Core 1 is allowed to boot without waiting for

configuration by an external master, while

core 0 is prevented from booting until

configured by an external master or the

other core.

10

Core 0 is allowed to boot without waiting for

configuration by an external master, while

core 1 is prevented from booting until

configured by an external master or the

other core.

11

Both cores are allowed to boot without

waiting for configuration by an external

master.

Signal name

LGPL3/LFWP, LGPL5

Function

Boot Sequencer

(cfg_boot_seq[0:1])

Select Option

PU / PD Resistors

Default value

11

Supported configuration

00

Reserved

01

Normal I2C addressing mode is used. Boot

sequencer is enabled and loads configuration

information from a ROM on the I2C 1

interface. A valid ROM must be present.

10

Extended I2C addressing mode Is used. Boot

sequencer is enabled and loads configuration

information from a ROM on the I2C 1

interface. A valid ROM must be present.

11

Boot sequencer is disabled. No I2C ROM is

accessed.