Figure 43. schematic diagram of the z-pan shield – Zilog ZUSBOPTS User Manual

Page 57

UM025603-0814

Schematic Diagrams

Zilog Educational Shields

User Manual

50

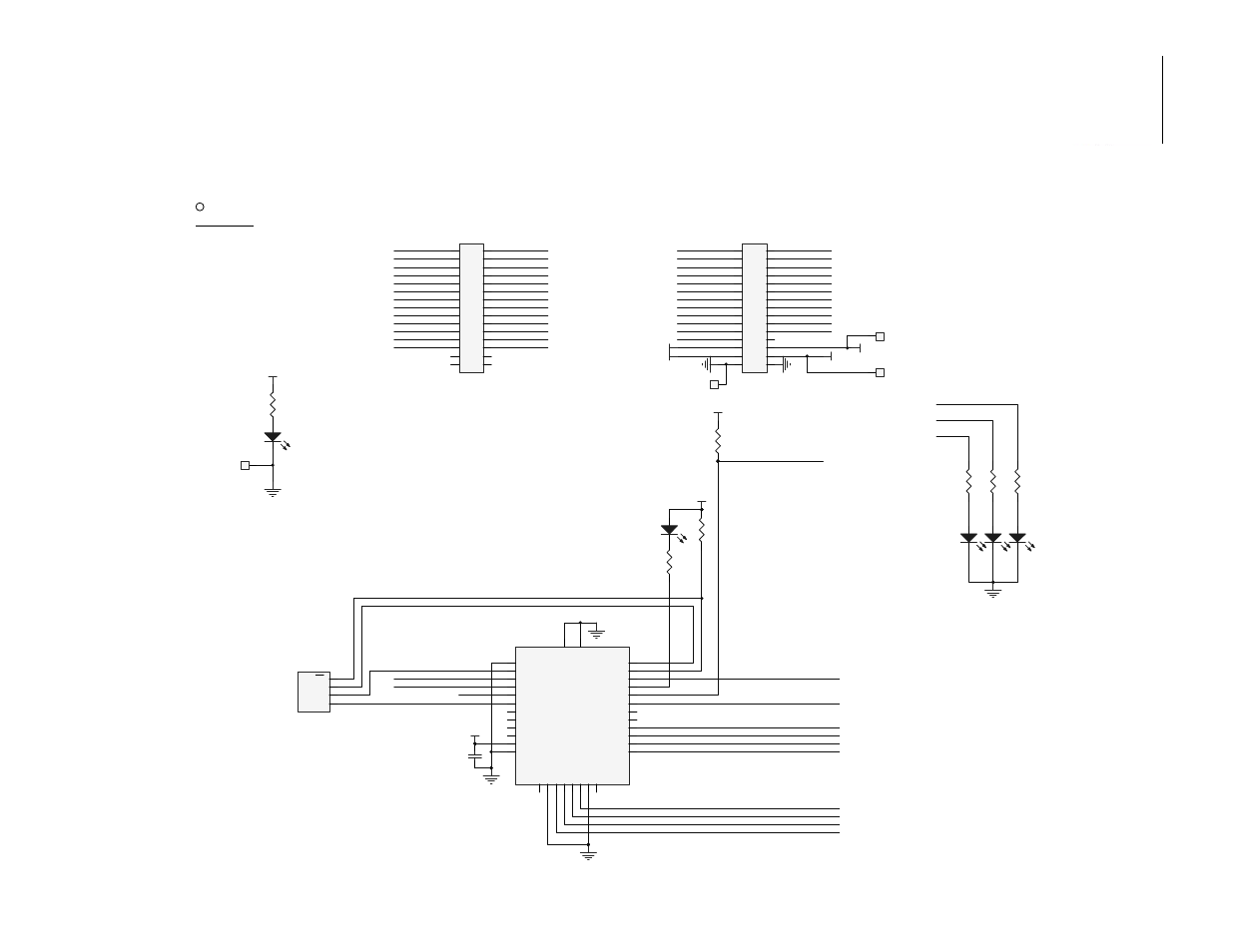

Figure 43 shows a schematic diagram of the ZED Z-PAN Shield.

Figure 43. Schematic Diagram of the Z-PAN Shield

BLU

LED1

.1uF

C1

3.3V

PD4

PD5

PD3

PD6

GRN

LED2

OUTPUT

PE7

PB5

PB4

RESET FACTORY DEFAULTS

DISCOVERY

HI=MASTER MODE

HI=115Kb

3.3V

PC2

(SS)

PC5

(MISO)

PC4

(MOSI)

(SCK)

PC3

3.3V

10K

R3

10K

R2

PB6

3.3V

1

A

P

0

A

P

3

A

P

2

A

P

5

A

P

4

A

P

7

A

P

6

A

P

1

B

P

0

B

P

3

B

P

2

B

P

5

B

P

4

B

P

7

B

P

6

B

P

1

C

P

0

C

P

3

C

P

2

C

P

5

C

P

4

C

P

7

C

P

6

C

P

1

D

P

0

D

P

3

D

P

2

D

P

5

D

P

4

D

P

7

D

P

6

D

P

1

E

P

0

E

P

3

E

P

2

E

P

5

E

P

4

E

P

7

E

P

6

E

P

VREF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

J1

2x15x2mm

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

J2

2x15x2mm

POWER

TP1

GND

SCLK

1

MOSI

2

MISO

3

SS

4

J3

SPI

PE5

PE6

CONNECT STATUS

GND

1

SPI MOSI

2

PIO6

3

PIO7

4

RESET

5

SPI_CLK

6

PCM_CLK

7

PCM_SYNC

8

PCM_IN

9

PCM_OUT

10

VDD

11

GND

12

UART_RX

13

UART_TX

14

UART_RTS

15

UART_CTS

16

USB_D+

17

USB_D-

18

PIO2

19

PIO3

20

PIO5

21

PIO4

22

SPI_CSB

23

SPI_MISO

24

GND

25

GND

27

GND

28

GND

29

AI

O0

30

PI

O

8

31

PI

O

9

32

PI

O

10

33

PI

O

11

34

AI

O1

35

RN-41

U1

PE0

PE1

PE2

PE3

RF(RX/TX) STATUS

Stacking Symbol

3.0K

R1

470

R4

KEY

TP3

GND

TP4

VMAIN

TP2

3.3V

3.3V

3.3V

VMAIN

VMAIN

TXD1

RXD1

CTS1-

DE1

PG3

7

F

P

6

F

P

1

H

P

0

H

P

3

H

P

2

H

P

PH4

I/O Lines Used

PE0

PE1

PE2

PE3

PE5

PE6

PB4

PB5

PB6

PC2

PC3

PC4

PC5

PD3

PD4

PD5

PD6

RED

LE

D

4

YE

L

LE

D

3

GRN

LE

D

5

PA2

PA1

PA0

PE7

PA0

PA1

PA2

470

R7

750

R6

1K

R5