Avalue EBM-CX700 User Manual

Page 59

User’s Manual

EBM-CX700 Series User’s Manual

59

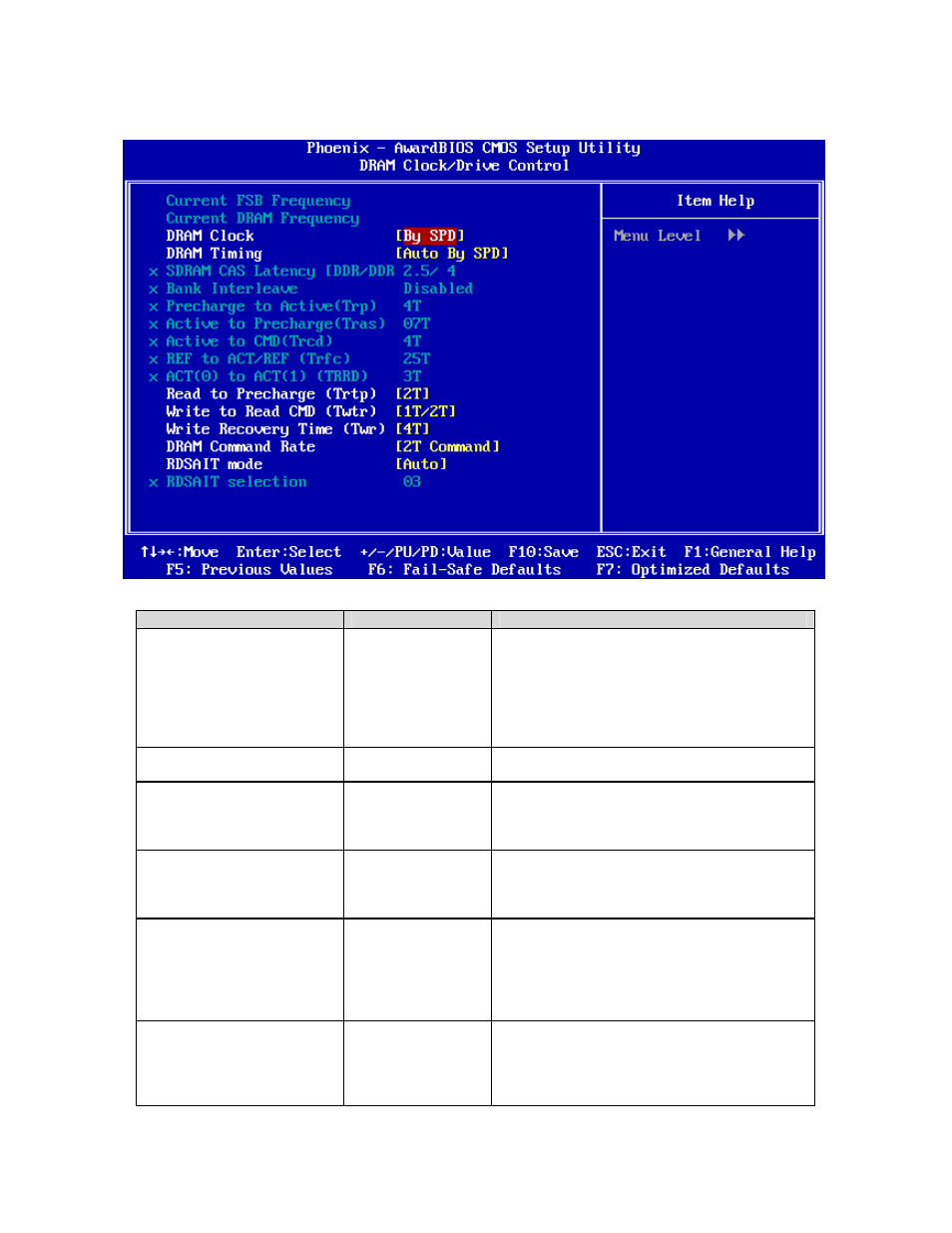

3.5.3.1 DRAM Clock/Drive Control

This section can set the DRAM clock/driver timing.

Item

Options

Description

DRAM Clock

By SPD

100NHz

133 MHz

166 MHz

200 MHz

266 MHz

333 MHz

Set the memory bus frequency to operate at

various values for the proper memory clock

setting

DRAM Timing

Manual

Auto By SPD

Set the memory timings for the said timings or

DRAM Cycle Lengths of 2 or 2.5.

SDRAM CAS Latency

1.5/2

2/3

2.5/4

3/5

This controls the time dealy passing before the

SDRAM starts to carry out a read command after

receiving it.

Bank Interleave

Diabled

2 Bank

4 Bank

8 Bank

Enables to set the interleave mode of the SDRM

interface which allows banks of SDRAM to

alternate their refresh and access cycles.

Precharge to Active(Trp)

2T

3T

4T

5T

This item sets the length of time taking to

precharge a row in the memory module before

a row being active and appears only when

DRAM timing

is set at Manual. Longer values

are safer but probably not acting the best

performance.

Active to Precharge(Tras)

05T, 06T,07T,08T,

09T,10T, 11T, 12T,

13T,14T, 15T, 16T,

17T,18T, 19T, 20T

This item sets the length of time that a row

staying active fore precharging and appears only

when DRAM timing is set at Manual. Longer

values are safer but probably not acting the best

performance.