South bridge chipset configuration – Avalue ECM-PNV User Manual

Page 68

ECM-PNV

68 ECM-PNV User

’s Manual

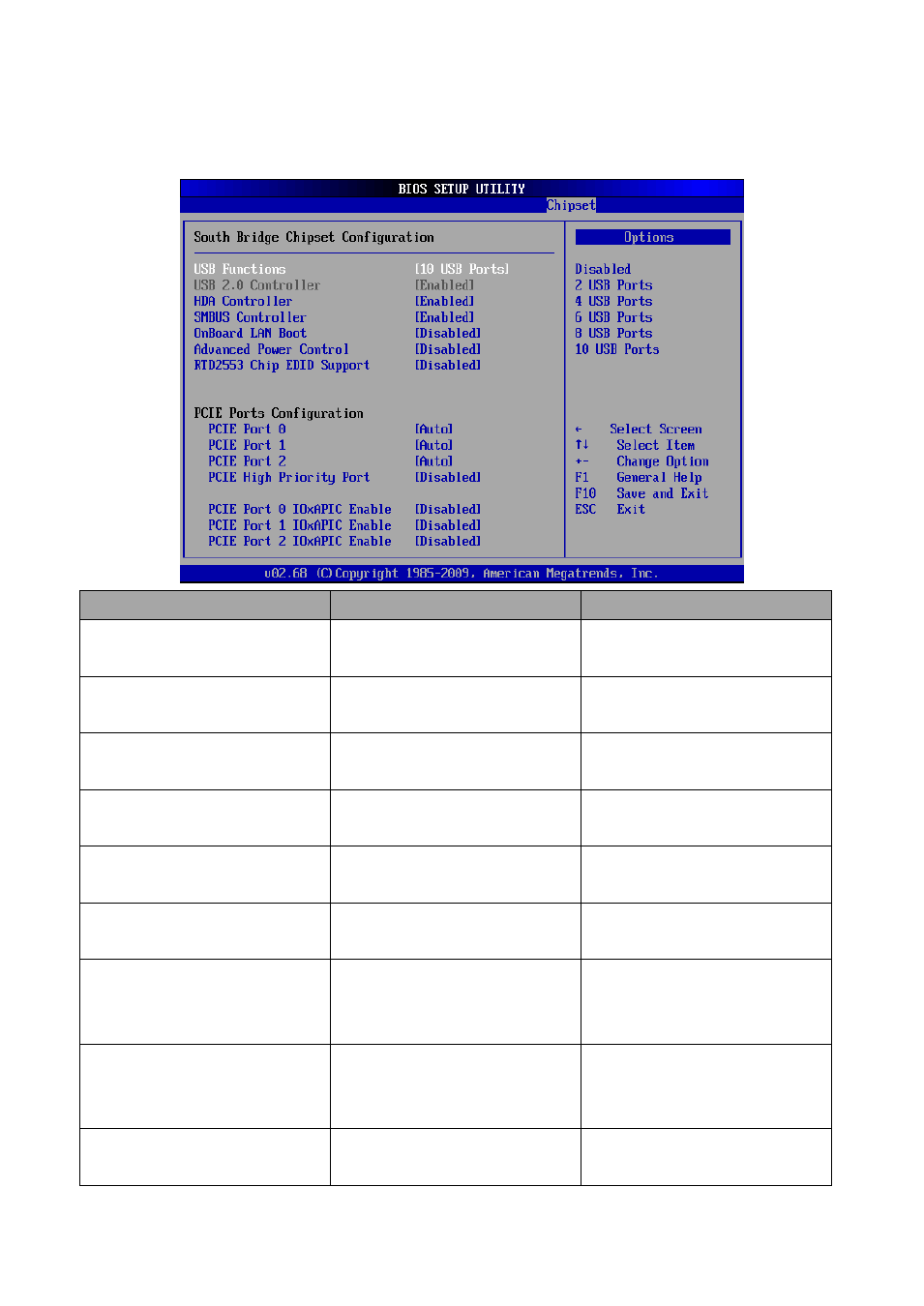

3.6.6.3 South bridge Chipset configuration

Use the Southbridge chipset configuration menu to configure Southbridge chipset

Item

Option

Description

USB Functions

Disables,

2/ 4/ 6/ 8/ 10 USB Ports

Enables the number of desired

ports or disables USB function.

USB 2.0 Controller [Enabled]

Disabled,

Enabled

This option is disabled by default.

HAD Controller [Enabled]

Disabled,

Enabled

Enable the Southbridge high

definition audio controller.

SMBUS Controller [Enabled]

Disabled,

Enabled

This option is enabled by default.

OnBoard LAN Boot [Disabled]

Disabled,

Enabled

This item helps to set onboard

LAN boot mode.

Advanced Power control

[Disabled]

Disabled

0/ 3/ 6/ 10

This option disables access to

Advanced Power control

PCIE Port 0/ 1/ 2/ 3/ 4 [Auto]

Disabled,

Enabled,

Auto

This section allows selecting

PCIE port 0/ 1/ 2/ 3/ 4 mode.

PCIE High Priority Port

[Disabled]

Disabled,

Enabled,

Auto

This item helps to set PCIE high

priority port.

PCIE Port 0/ 1/ 2/ 3/ 4 IOxAPIC

Enable [Disabled]

Disabled,

Enabled

This helps to enable or disable

PCIE port 0/ 1/ 2/ 3/ 4 IOxAPIC.