3 ssi_trig2 and ssi_start_op – ADLINK PCI-9820 User Manual

Page 39

Operation Theory

• 29

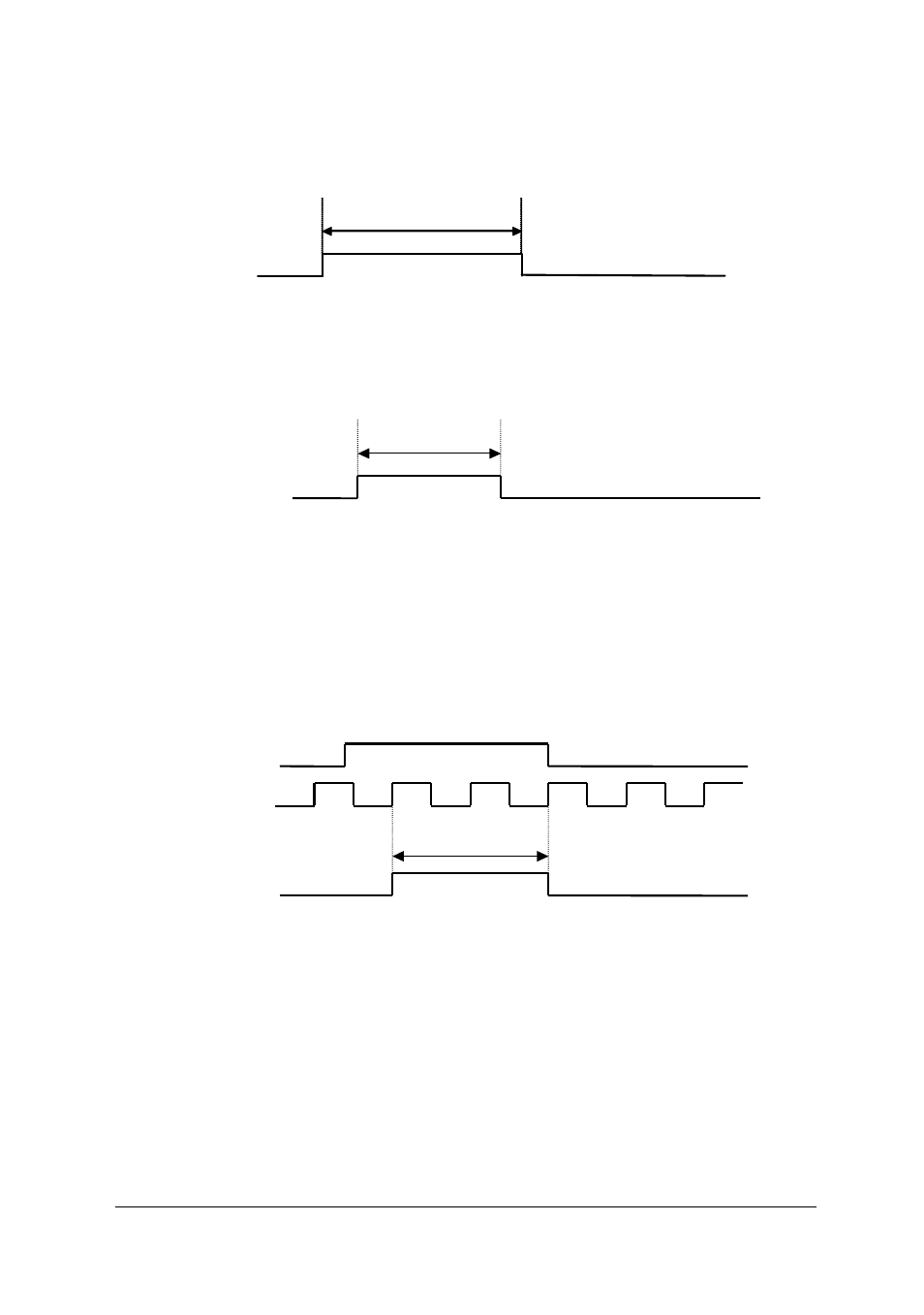

Fig 4.12 and Fig 4.13 show the input and output timing requirements.

T

w

SSI_TRIG1

T

w

= 2 - 3 TIMEBASE clocks

Figure 4.12 SSI_TRIG1 output signal timing

T

w

SSI_TRIG1

T

w

= 20 ns minimum

Figure 4.13 SSI_TRIG1 input signal timing

4.7.3

SSI_TRIG2 and SSI_START_OP

As an output, the SSI_TRIG2 signal is a clocked SSI_TRIG1 signal by

TIMEBASE, as illustrated in Fig 4.14.

T

w

SSI_TRIG1

T

w

= 2 TIMEBASE clocks

SSI_TRIG2

TIMEBASE

Figure 4.14 SSI_TRIG2 output signal timing

As an input, the PCI-9820 accepts the SSI_TRIG2 signal to be the source of

a one-clock delayed trigger event. The controller on the PCI-9820 will then

compensate the one-clock delay if using SSI_TRIG2 as the source of trigger

event. The signal is configured in the rising edge-detection mode.

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (92 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)