2 a/d data registers – ADLINK ACL-8111 User Manual

Page 25

Registers Format

• 19

3.2 A/D Data Registers

ACL-8111 provides 8 single-end A/D input channels. The 12 bit A/D data is

put in two 8-bit registers. The low byte date (8 LSBs) is at address BASE+4

and the high byte data (4 MSBs) is at address BASE+5. The DRDY bit is

used to indicate the status of A/D conversion. DRDY goes to low-level

means A/D conversion is completed.

Address : BASE + 4 and BASE + 5

Attribute: read only

Data Format:

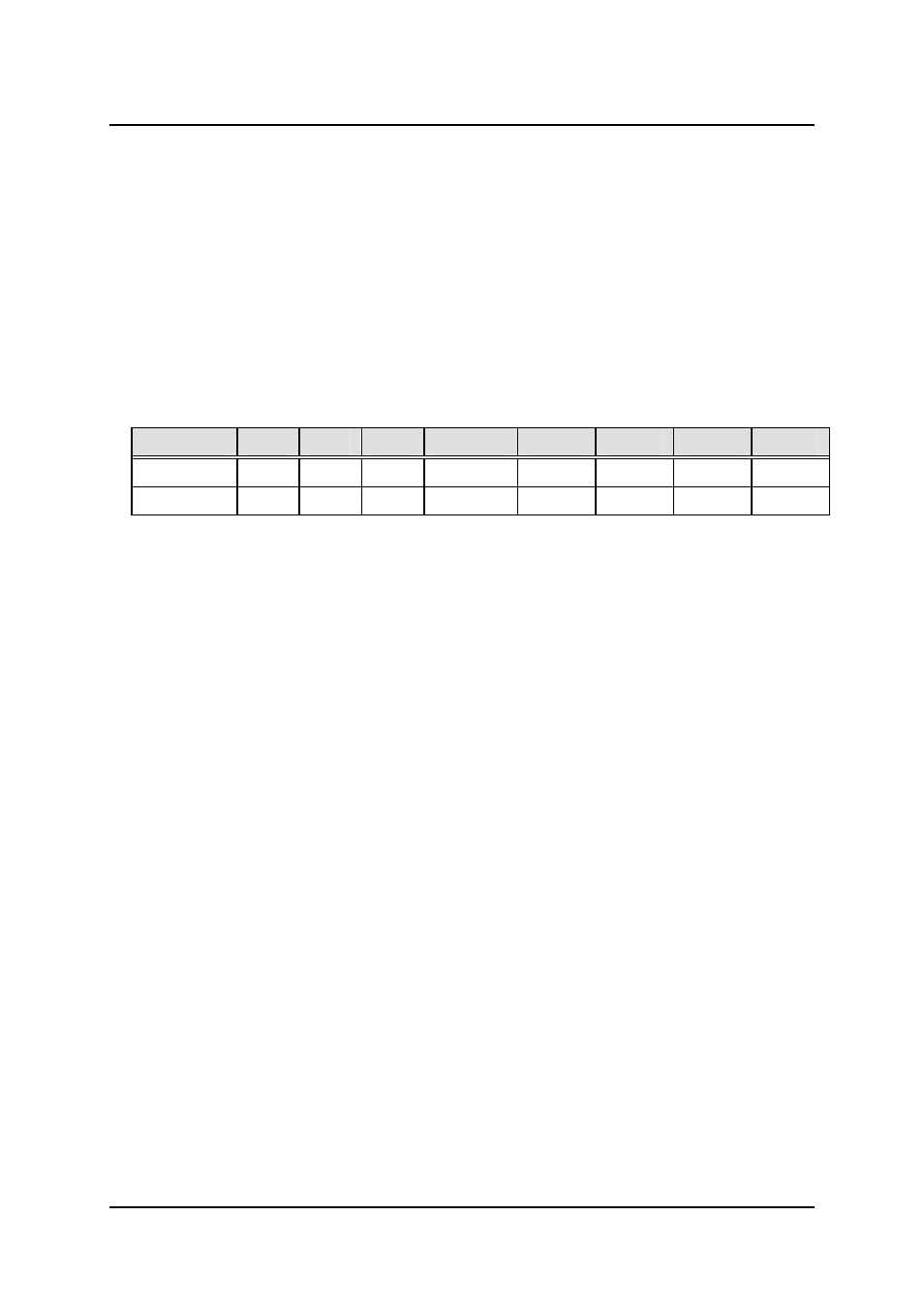

Bit

7

6

5

4

3

2

1

0

BASE+4

AD7

AD6

AD5 AD4 AD3 AD2 AD1 AD0

BASE+5 0 0 0 DRDY

AD11 AD10 AD9 AD8

AD11. AD0: Analog to digital data. AD11 is the Most Significant Bit (MSB).

AD0 is the Least Significant Bit (LSB).

DRDY: Data Ready Signal.

1: A/D data is not ready

0: A/D conversion is completed.

It will be set to 1 after reading out the low byte data

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- PCM-9112+ (10 pages)

- PCM-9112+ (94 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (4 pages)

- PCM-6308V+ (52 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (82 pages)

- cPCI-7300 (83 pages)