8 internal/external trigger setting – ADLINK ACL-8112 Series User Manual

Page 25

Installation

• 17

2.8

Internal/External Trigger Setting

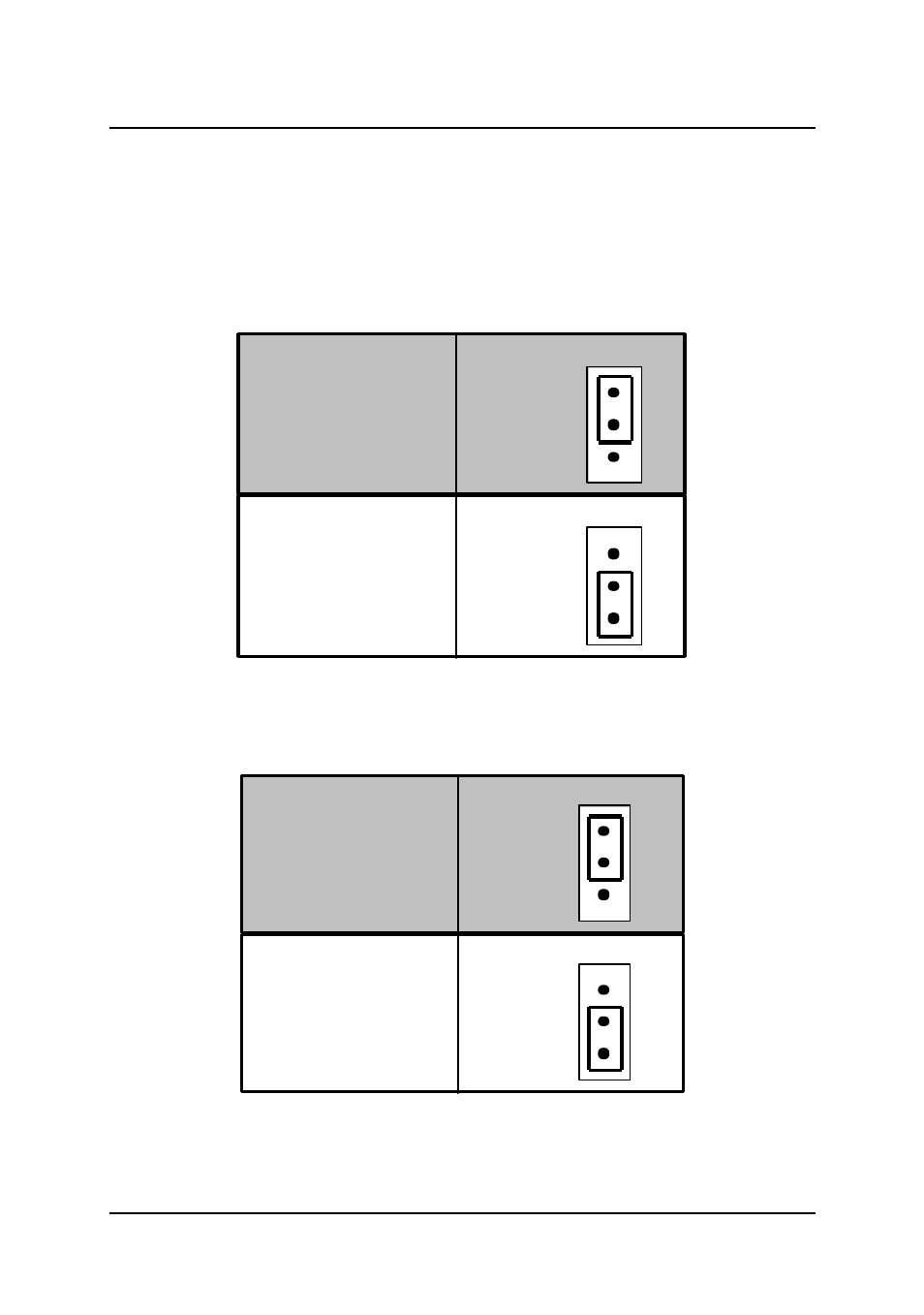

The A/D conversion trigger source of the ACL-8112 can come from an

internal or external source. The internal or external trigger source is set by

JP4 on the ACL-8112DG/HG and by JP5 on the ACL-8112PG, as shown

on Figure 2.5. Note that there are two internal trigger sources, one is by

software trigger and the other is by the programmable pacer trigger, which

is controlled by the mode control register(see section 4.5).

Figure 2.5 Trigger Source Setting

Figure 2.6 Timer's Clock Source Setting

Internal Trigger

(default setting)

External Trigger

JP4 / JP5

INTTRG

EXTTRG

JP4 / JP5

INTTRG

EXTTRG

Internal Clock

Source : 2MHz

(default setting)

External Clock

Source

JP6 / JP4

INTCLK

EXTCLK

JP6 / JP4

INTCLK

EXTCLK

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (94 pages)

- PCM-9112+ (10 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (83 pages)

- cPCI-7300 (82 pages)