Cypress CY7C09079V User Manual

Page 17

CY7C09079V/89V/99V

CY7C09179V/89V/99V

Document #: 38-06043 Rev. *C

Page 17 of 21

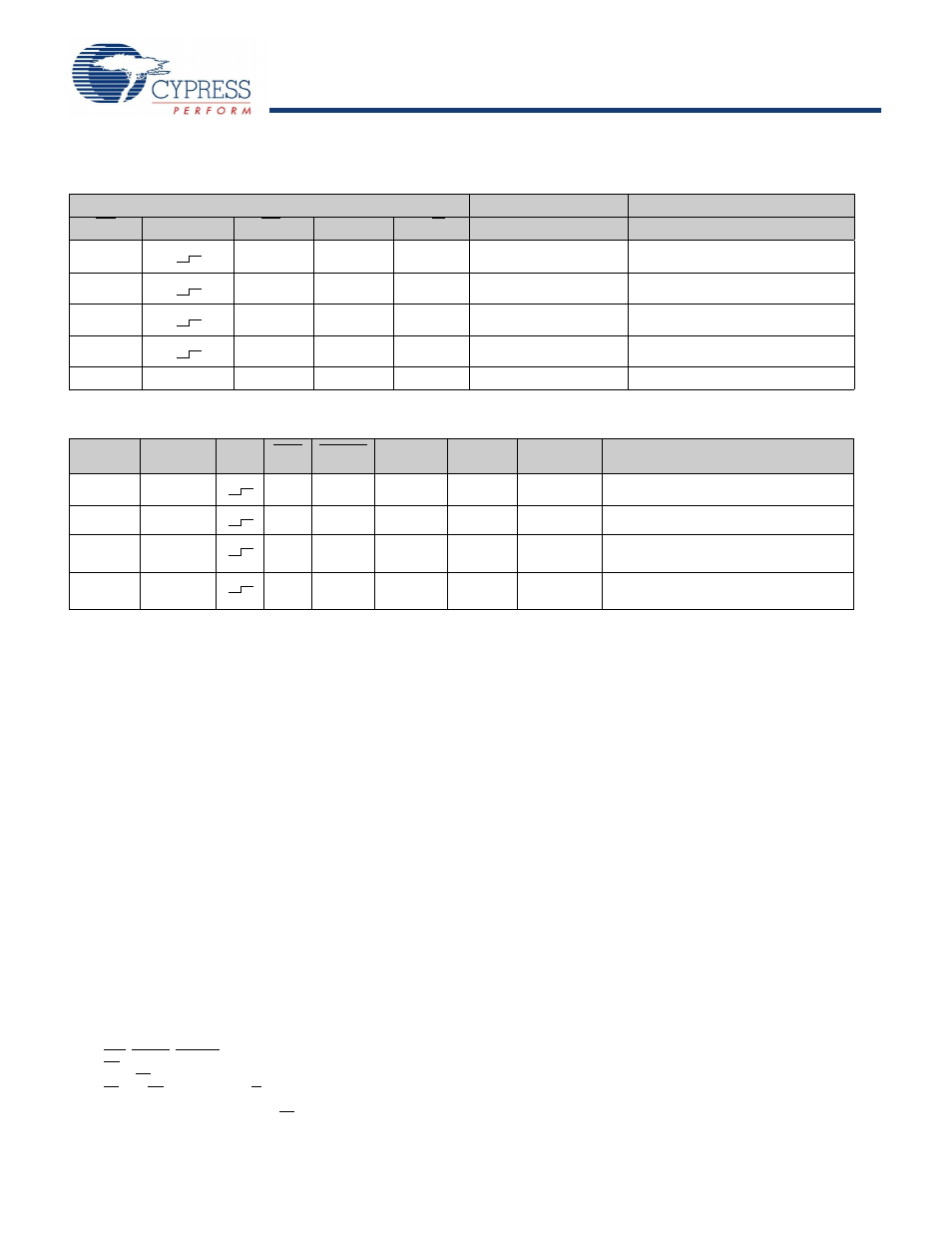

Table 1. Read/Write and Enable Operation

Inputs

Outputs

OE

CLK

CE

0

CE

1

R/W

I/O

0

–I/O

9

Operation

X

H

X

X

High-Z

Deselected

X

X

L

X

High-Z

Deselected

X

L

H

L

D

IN

Write

L

L

H

H

D

OUT

Read

H

X

L

H

X

High-Z

Outputs Disabled

Table 2. Address Counter Control Operation

Address Previous

Address

CLK

ADS

CNTEN CNTRST

I/O

Mode

Operation

X

X

X

X

L

D

out(0)

Reset

Counter Reset to Address 0

A

n

X

L

X

H

D

out(n)

Load

Address Load into Counter

X

A

n

H

H

H

D

out(n)

Hold

External Address Blocked—Counter

Disabled

X

A

n

H

L

H

D

out(n+1)

Increment

Counter Enabled—Internal Address

Generation

Notes

34. “X” = “Don’t Care”, “H” = V

IH

, “L” = V

IL

.

35. ADS, CNTEN, CNTRST = “Don’t Care.”

36. OE is an asynchronous input signal.

37. When CE changes state in the pipelined mode, deselection and read happen in the following clock cycle.

38. CE

0

and OE = V

IL

; CE

1

and R/W = V

IH

.

39. Data shown for flow-through mode; pipelined mode output will be delayed by one cycle.

40. Counter operation is independent of CE

0

and CE

1

.