Initial line state configuration – Maxim Integrated 73M1866B/73M1966B Implementers Guide User Manual

Page 15

UG_1x66B_016

73M1866B/73M1966B Implementer’s Guide

Rev. 1.3

15

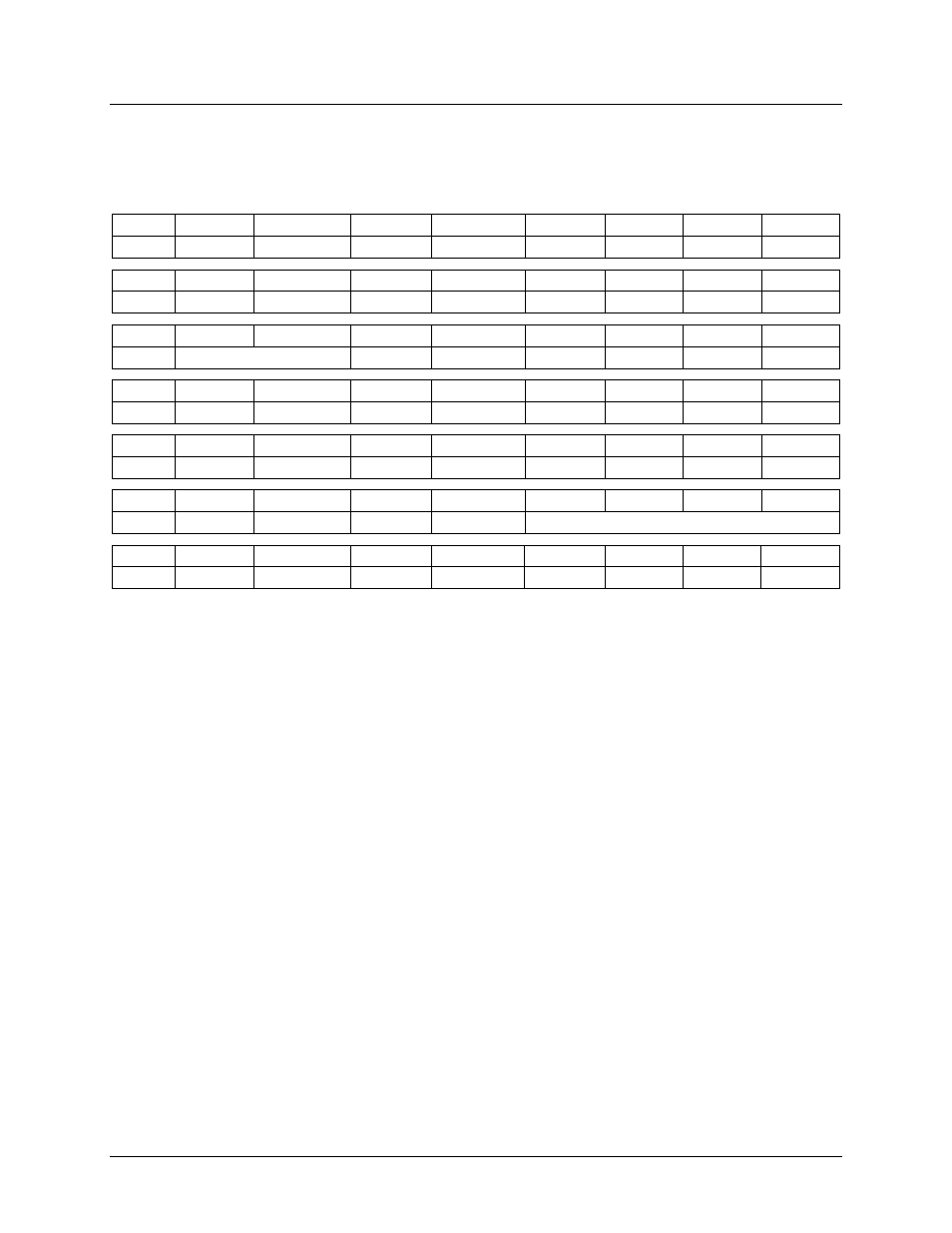

3.2.3 Initial Line State Configuration

The default condition of the device is to be on hook after reset and startup.

The registers used in this procedure are:

0x05

ENGPIO7 ENGPIO6

ENGPIO5 ENPCLKDT ENAPOL

ENDET

ENSYNL ENRGDT

Write

X

X

X

X

1

X

1

X

0x12

OFH

ENDC

ENAC

ENSHL

ENLVD

ENFEL

ENDT

ENNOM

Write

0

0

0

0

0

1

0

0

0x13

DCIV1

DCIV0

ILM

RSVD

PLDM

OVDTH

IDISPD

Res

Write

VAL1[1:0]

0

0

0

0

0

0

0x14

TXBST

DAA1

DAA0

Res

RXBST

RLPNH

RXG1

RXG0

Write

X

X

X

0

X

X

X

X

0x15

ENOLD

DISNTR

Res

CIDM

THEN

ENUVD

ENOVD

ENOID

Write

0

0

0

0

1

0

0

0

0x16

TXEN

RXEN

RLPNEN

ATEN

ACZ3

ACZ2

ACZ1

ACZ0

Write

1

1

0

1

VAL2[3:0]

0x17

Res

Res

RXOCEN

Res

Res

Res

Res

Res

Write

0

0

0

0

0

0

0

0

The temporary variables defined in this procedure are:

VAL1 = Set the DCIV bits to the desired DC current voltage characteristic as defined in the

73M1866B/73M1966B Data Sheet.

VAL2 = System appropriate value for ACZ[3:0].

Begin

1. Set ENAPOL =1 and ENSYNL = 1, to allow automatic polling of line side registers (write RG05 =

xxxx_1x1x).

2. Set ENFEL = 1, OFH = ENDC = ENAC = ENSHL =

ENVLD = ENDT = ENNOM = 0 (Write RG12 =

0x40).

3. Set ILM = RSVD = PLDM = OVDTH = IDISPD = Res = 0, DCIV = VAL1 (Write RG13 =

Val1[1:0]00_0000).

4. Write RG14 = xxx0_xxxx.

5. Set THEN = 1, set ENOLD = DISNTR = CHPSEN = CIDM = ENUVD = ENOVD = ENOID = 0 (Write

RG15 = 0000_1000).

6. Set TXEN = RXEN = ATEN = 1, RLPNEN = 0 and ACZ[3:0] =VAL2[3:0] (Write RG16 =

1101_VAL2[3:0]).

7. Set RXOCEN and all Res bits in RG17 = 0 (write RG17 = 0x00).

End

After this point the host may selectively enable other on-hook operations such as ring detection or CID

mode.