Cypress CY7C1347G User Manual

Functional description, Selection guide, Features

CY7C1347G

4-Mbit (128K x 36) Pipelined Sync SRAM

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document #: 38-05516 Rev. *F

Revised January 15, 2009

Features

■

Fully registered inputs and outputs for pipelined operation

■

128K x 36 common IO architecture

■

3.3V core power supply (V

DD

)

■

2.5V/3.3V IO power supply (V

DDQ

)

■

Fast clock to output times: 2.6 ns (for 250 MHz device)

■

User-selectable burst counter supporting Intel

®

Pentium

®

interleaved or linear burst sequences

■

Separate processor and controller address strobes

■

Synchronous self-timed writes

■

Asynchronous output enable

■

Offered in Pb-free 100-Pin TQFP, Pb-free and non Pb-free

119-Ball BGA package, and 165-Ball FBGA package

■

“ZZ” sleep mode option and stop clock option

■

Available in industrial and commercial temperature ranges

Functional Description

The CY7C1347G is a 3.3V, 128K x 36 synchronous-pipelined

SRAM designed to support zero-wait-state secondary cache

with minimal glue logic. CY7C1347G IO pins can operate at

either the 2.5V or the 3.3V level. The IO pins are 3.3V tolerant

when V

DDQ

= 2.5V. All synchronous inputs pass through input

registers controlled by the rising edge of the clock. All data

outputs pass through output registers controlled by the rising

edge of the clock. Maximum access delay from the clock rise is

2.6 ns (250 MHz device). CY7C1347G supports either the

interleaved burst sequence used by the Intel Pentium processor

or a linear burst sequence used by processors such as the

PowerPC

®

. The burst sequence is selected through the MODE

pin. Accesses can be initiated by asserting either the Address

Strobe from Processor (ADSP) or the Address Strobe from

Controller (ADSC) at clock rise. Address advancement through

the burst sequence is controlled by the ADV input. A 2-bit on-chip

wraparound burst counter captures the first address in a burst

sequence and automatically increments the address for the rest

of the burst access.

Byte write operations are qualified with the four Byte Write Select

(BW

[A:D]

) inputs. A Global Write Enable (GW) overrides all byte

write inputs and writes data to all four bytes. All writes are

conducted with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Selects (CE

1

, CE

2

, CE

3

) and an

asynchronous Output Enable (OE) provide for easy bank

selection and output tri-state control. To provide proper data

during depth expansion, OE is masked during the first clock of a

read cycle when emerging from a deselected state.

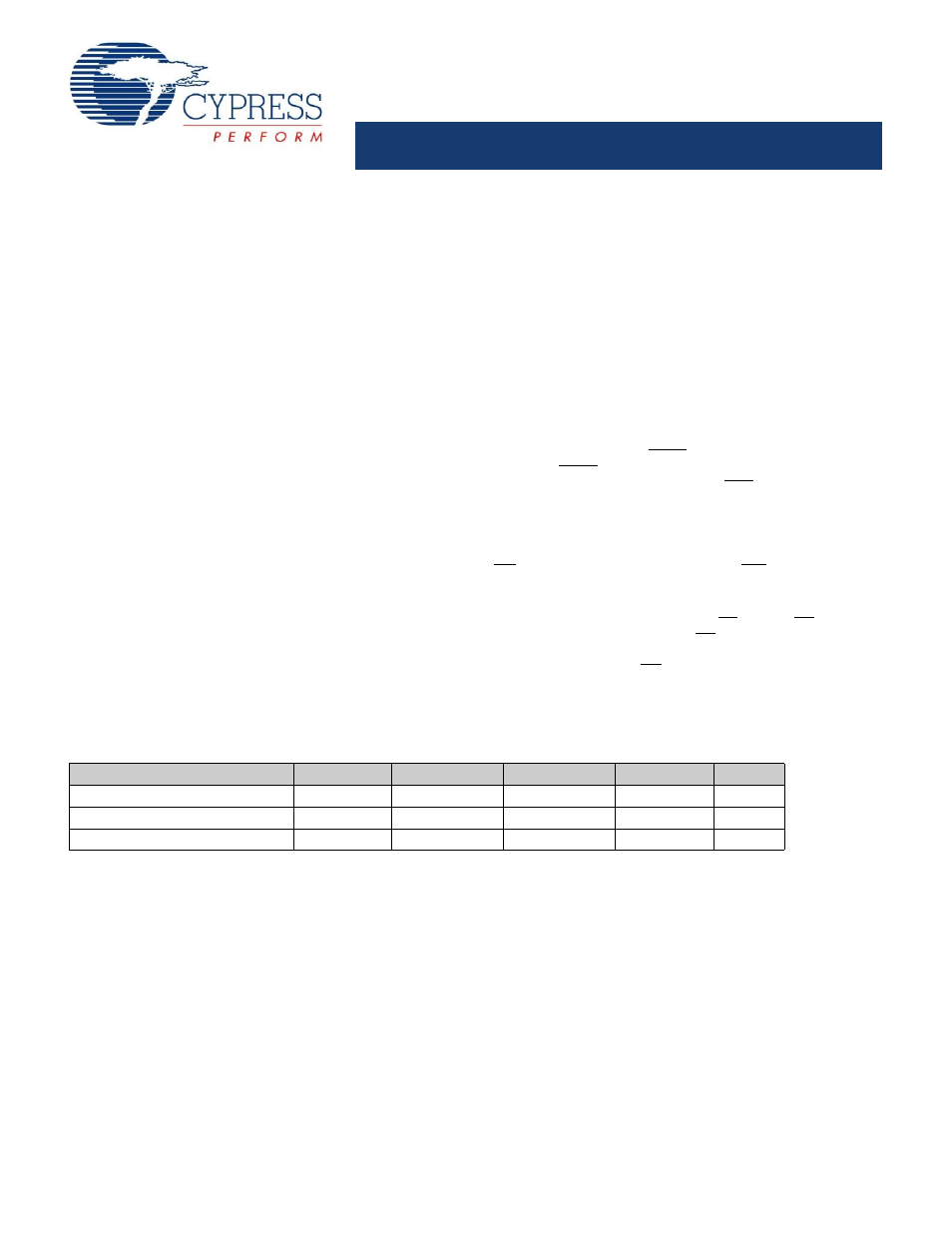

Selection Guide

Specification

250 MHz

200 MHz

166 MHz

133 MHz

Unit

Maximum Access Time

2.6

2.8

3.5

4.0

ns

Maximum Operating Current

325

265

240

225

mA

Maximum CMOS Standby Current

40

40

40

40

mA

Note

1. For best practice recommendations, refer to the Cypress application note

.

Document Outline

- Functional Description[1]

- Selection Guide

- Block Diagram

- Pinouts

- Functional Overview

- Maximum Ratings

- Operating Range

- Electrical Characteristics

- Capacitance

- Thermal Resistance

- AC Test Loads and Waveforms

- Switching Characteristics

- Switching Waveforms

- Ordering Information

- Package Diagrams

- Document History Page

- Sales, Solutions, and Legal Information