Digilent 210-179P User Manual

Page 2

VmodCAM Reference Manual

www.digilentinc.com

page 2 of 6

Copyright Digilent, Inc. All rights reserved. Other product and company names mentioned may be trademarks of their respective owners.

First, you must set up the power-up and reset

sequence. Then you need to understand the

control interface in order to configure the

cameras. The following sections describe this

in detail.

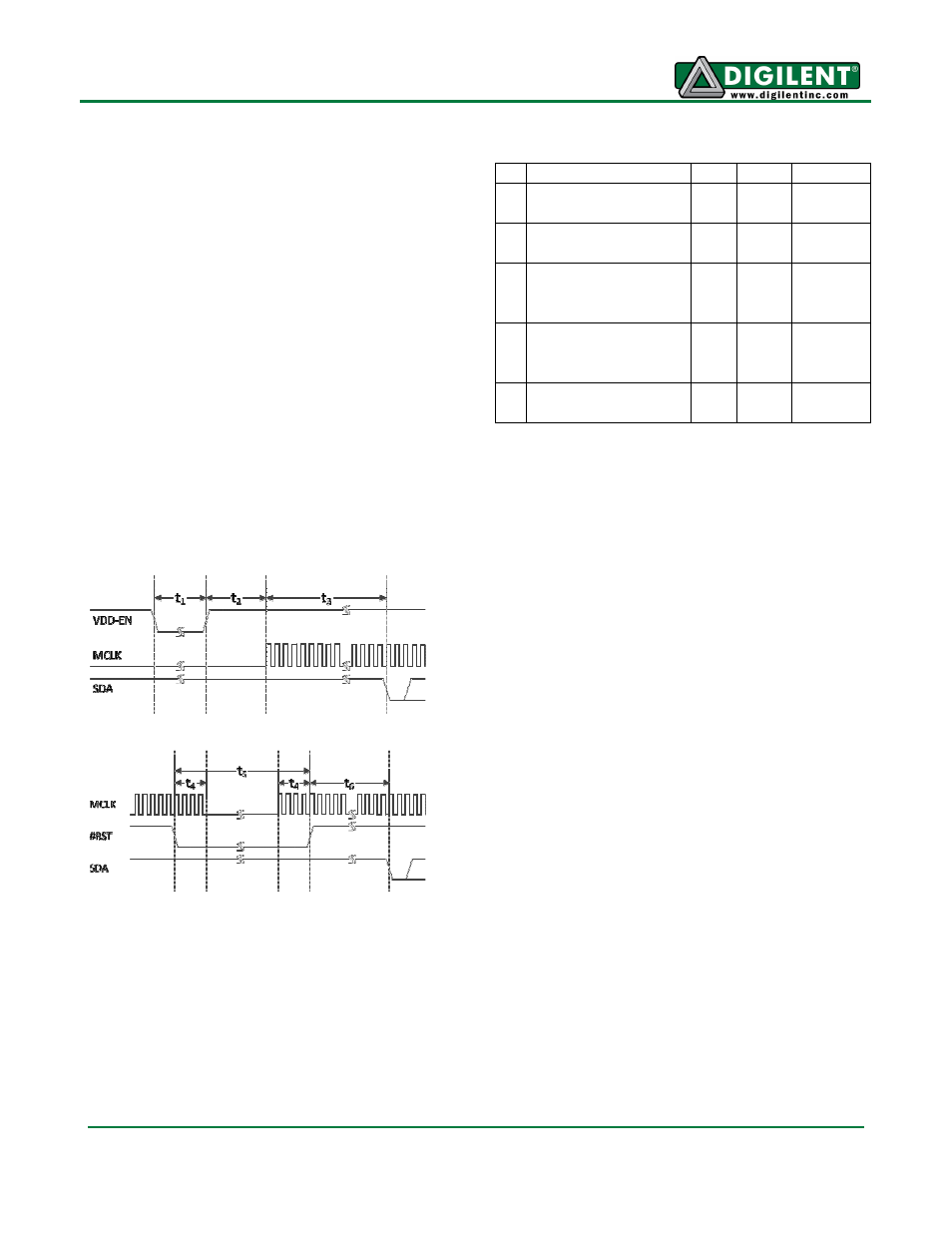

Power-Up and Reset Sequence

The VmodCAM should only be attached to the

system board once the signals driven by the

system board are defined.

The camera uses the analog and digital supply

voltage rails provided on-board. The power

supplies are on by default, but can be turned

off, by driving the VDD-EN signal low (see

Table 3.)

The power supplies are used by both cameras.

While the cameras do power-on reset

themselves, it’s always a good idea to do a full

reset as part of the controller routine.

Figure 1 Power-Up Sequence

Figure 2 Reset Sequence

The MCLK is important. If the PLL in the

camera is enabled, MCLK should be stable.

Stopping MCLK without respecting the reset

sequence might leave the camera in an

undefined state. This could be the case when

the FPGA is re-configured. Performing a

power-cycle in the first stages of the controller

is recommended.

Description

Min Max

Unit

t1 VDD-EN negative

pulse width

100

ms

t2 VDD-EN high to

first MCLK pulse

75

us

t3

t6

ROM read time

until first control

byte

6000

MCLK

cycles

t4 Active MCLK

before/after #RST

edge

10

MCLK

cycles

t5 #RST negative

pulse width

30

MCLK

cycles

Table 1 Power-Up/Reset Timing

Control Interface

The two-wire serial interface (SDA, SCL) can

be used to control various parts of the camera.

The camera acts as a slave device.

A typical register write consists of:

•

start condition

•

8-bit device address (0x78 for the

MT9D112) + acknowledge bit

•

upper byte of 16-bit register address +

acknowledge bit

•

lower byte of register address +

acknowledge bit

•

upper byte of the 16-bit data +

acknowledge bit

•

lower data byte + acknowledge bit

•

stop condition.