Cypress CY7C1361C User Manual

Page 8

CY7C1361C

CY7C1363C

Document #: 38-05541 Rev. *F

Page 8 of 31

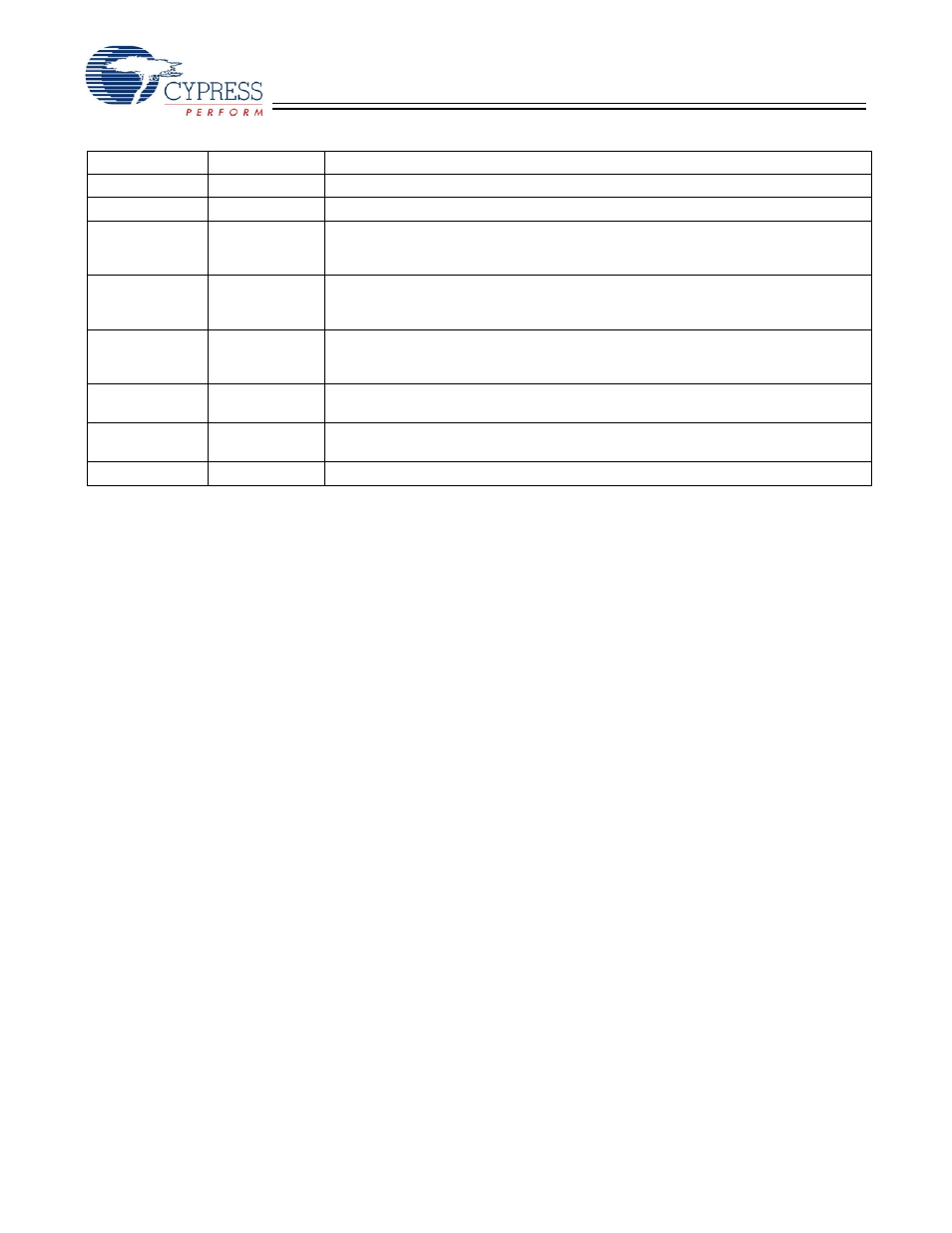

V

SS

Ground

Ground for the core of the device.

V

SSQ

I/O Ground

Ground for the I/O circuitry.

TDO

JTAG serial output

Synchronous

Serial data-out to the JTAG circuit. Delivers data on the negative edge of TCK. If the

JTAG feature is not being utilized, this pin should be left unconnected. This pin is not

available on TQFP packages.

TDI

JTAG serial input

Synchronous

Serial data-In to the JTAG circuit. Sampled on the rising edge of TCK. If the JTAG

feature is not being utilized, this pin can be left floating or connected to V

DD

through a pull

up resistor. This pin is not available on TQFP packages.

TMS

JTAG serial input

Synchronous

Serial data-In to the JTAG circuit. Sampled on the rising edge of TCK. If the JTAG

feature is not being utilized, this pin can be disconnected or connected to V

DD

. This pin

is not available on TQFP packages.

TCK

JTAG-

Clock

Clock input to the JTAG circuitry. If the JTAG feature is not being utilized, this pin must

be connected to V

SS

. This pin is not available on TQFP packages.

NC

–

No Connects. Not internally connected to the die. 18M, 36M, 72M, 144M, 288M, 576M

and 1G are address expansion pins and are not internally connected to the die.

V

SS

/DNU

Ground/DNU

This pin can be connected to Ground or should be left floating.

Pin Definitions

(continued)

Name

I/O

Description