Switching characteristics, Is shown in, Switching – Cypress CY7C1316JV18 User Manual

Page 22: Characteristics

CY7C1316JV18, CY7C1916JV18

CY7C1318JV18, CY7C1320JV18

Document Number: 001-15271 Rev. *B

Page 22 of 26

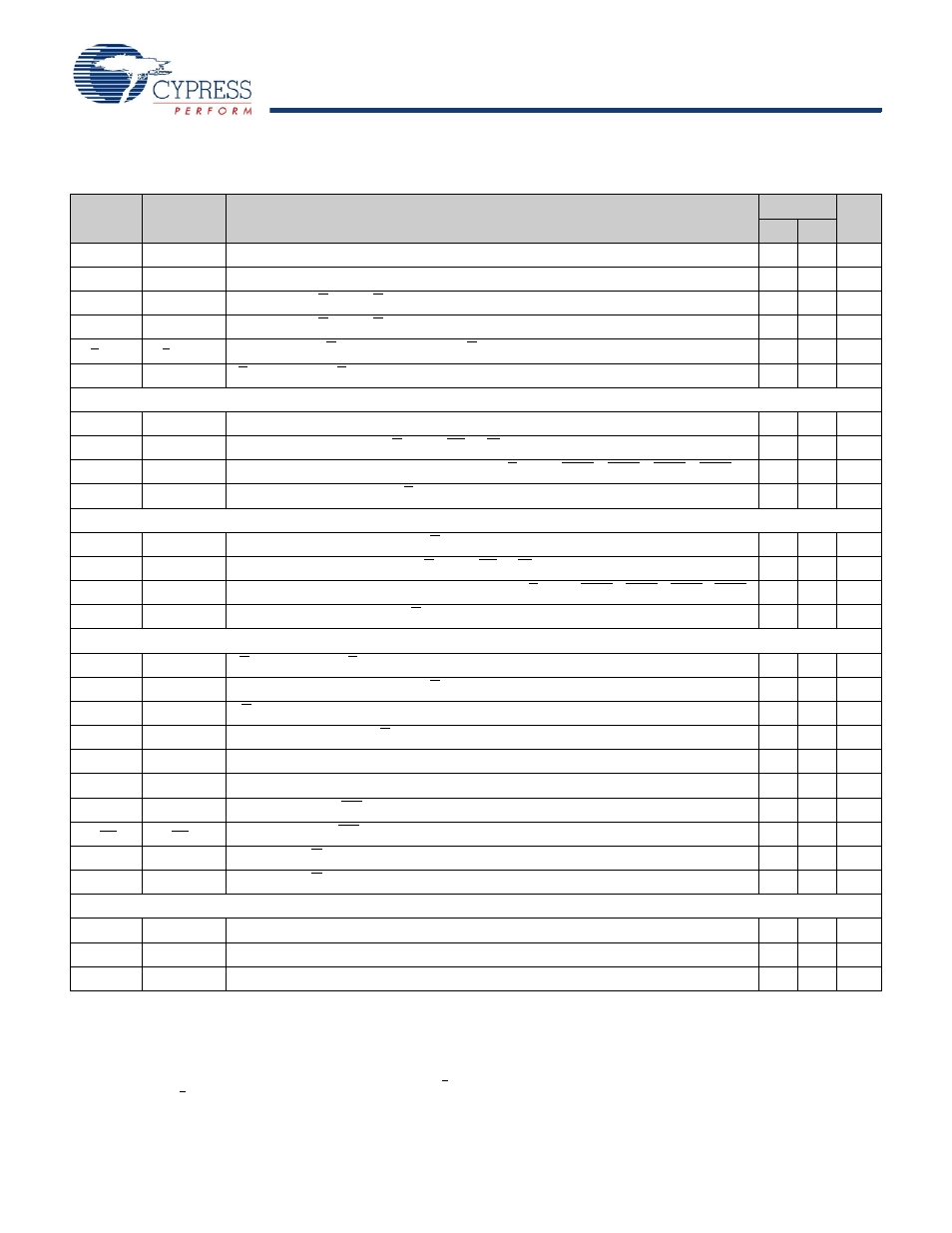

Switching Characteristics

Over the Operating Range

Cypress

Parameter

Consortium

Parameter

Description

300 MHz

Unit

Min

Max

t

POWER

V

DD

(Typical) to the first Access

1

–

ms

t

CYC

t

KHKH

K Clock and C Clock Cycle Time

3.30

8.4

ns

t

KH

t

KHKL

Input Clock (K/K and C/C) HIGH

1.32

–

ns

t

KL

t

KLKH

Input Clock (K/K and C/C) LOW

1.32

–

ns

t

KHKH

t

KHKH

K Clock Rise to K Clock Rise and C to C Rise (rising edge to rising edge)

1.49

–

ns

t

KHCH

t

KHCH

K/K Clock Rise to C/C Clock Rise (rising edge to rising edge)

0.00 1.45

ns

Setup Times

t

SA

t

AVKH

Address Setup to K Clock Rise

0.4

–

ns

t

SC

t

IVKH

Control Setup to Clock (K, K) Rise (LD, R/W)

0.4

–

ns

t

SCDDR

t

IVKH

Double Data Rate Control Setup to Clock (K, K) Rise (BWS

0

, BWS

1

, BWS

2

, BWS

3

)

0.3

–

ns

t

SD

t

DVKH

D

[X:0]

Setup to Clock (K and K) Rise

0.3

–

ns

Hold Times

t

HA

t

KHAX

Address Hold after Clock (K and K) Rise

0.4

–

ns

t

HC

t

KHIX

Control Hold after Clock (K and K) Rise (LD, R/W)

0.4

–

ns

t

HCDDR

t

KHIX

Double Data Rate Control Hold after Clock (K and K) Rise (BWS

0

, BWS

1

, BWS

2

, BWS

3

) 0.3

–

ns

t

HD

t

KHDX

D

[X:0]

Hold after Clock (K and K) Rise

0.3

–

ns

Output Times

t

CO

t

CHQV

C/C Clock Rise (or K/K in single clock mode) to Data Valid

–

0.45

ns

t

DOH

t

CHQX

Data Output Hold after Output C/C Clock Rise (Active to Active)

–0.45

–

ns

t

CCQO

t

CHCQV

C/C Clock Rise to Echo Clock Valid

–

0.45

ns

t

CQOH

t

CHCQX

Echo Clock Hold after C/C Clock Rise

–0.45

–

ns

t

CQD

t

CQHQV

Echo Clock High to Data Valid

–

0.27

ns

t

CQDOH

t

CQHQX

Echo Clock High to Data Invalid

–0.27

–

ns

t

CQH

t

CQHCQL

Output Clock (CQ/CQ) HIGH

1.24

–

ns

t

CQHCQH

t

CQHCQH

CQ Clock Rise to CQ Clock Rise (rising edge to rising edge)

1.24

–

ns

t

CHZ

t

CHQZ

Clock (C and C) Rise to High-Z (Active to High-Z)

–

0.45

ns

t

CLZ

t

CHQX1

Clock (C and C) Rise to Low-Z

–0.45

–

ns

DLL Timing

t

KC Var

t

KC Var

Clock Phase Jitter

–

0.20

ns

t

KC lock

t

KC lock

DLL Lock Time (K, C)

1024

–

Cycles

t

KC Reset

t

KC Reset

K Static to DLL Reset

30

–

ns

Notes

20. This part has an internal voltage regulator; t

POWER

is the time that the power is supplied above V

DD

minimum initially before a read or write operation can be initiated.

21. These parameters are extrapolated from the input timing parameters (t

KHKH

- 250 ps, where 250 ps is the internal jitter. An input jitter of 200 ps (t

KC Var

) is already

included in the t

KHKH

). These parameters are only guaranteed by design and are not tested in production.

22. t

CHZ

, t

CLZ

are specified with a load capacitance of 5 pF as in (b) of

. Transition is measured

±100 mV from steady-state voltage.

23. At any voltage and temperature t

CHZ

is less than t

CLZ

and t

CHZ

less than t

CO

.