Cypress CY7C028V User Manual

Features, Logic block diagram

CY7C027V/027VN/027AV/028V

CY7C037V/037AV/038V

3.3V 32K/64K x 16/18 Dual-Port Static

RAM

Cypress Semiconductor Corporation

•

198 Champion Court

•

San Jose

,

CA 95134-1709

•

408-943-2600

Document #: 38-06078 Rev. *B

Revised December 09, 2008

Features

■

True Dual-Ported memory cells which allow

simultaneous access of the same memory location

■

32K x 16 organization (CY7C027V/027VN/027AV

)

■

64K x 16 organization (CY7C028V)

■

32K x 18 organization (CY7C037V/037AV

)

■

64K x 18 organization (CY7C038V)

■

0.35 micron CMOS for optimum speed and power

■

High speed access: 15, 20, and 25 ns

■

Low operating power

■

Active: I

CC

= 115 mA (typical)

■

Standby: I

SB3

= 10

μA (typical)

■

Fully asynchronous operation

■

Automatic power down

■

Expandable data bus to 32/36 bits or more using Master/Slave

chip select when using more than one device

■

On-chip arbitration logic

■

Semaphores included to permit software handshaking

between ports

■

INT flag for port-to-port communication

■

Separate upper-byte and lower-byte control

■

Dual chip enables

■

Pin select for Master or Slave

■

Commercial and Industrial temperature ranges

■

100-pin Pb-free TQFP and 100-pin TQFP

Notes

1. CY7C027V, CY7C027VN and CY7C027AV are functionally identical.

2. CY7C037V and CY7C037AV are functionally identical.

3. I/O

8

–I/O

15

for x16 devices; I/O

9

–I/O

17

for x18 devices.

4. I/O

0

–I/O

7

for x16 devices; I/O

0

–I/O

8

for x18 devices.

5. A

0

–A

14

for 32K; A

0

–A

15

for 64K devices.

6. BUSY is an output in master mode and an input in slave mode.

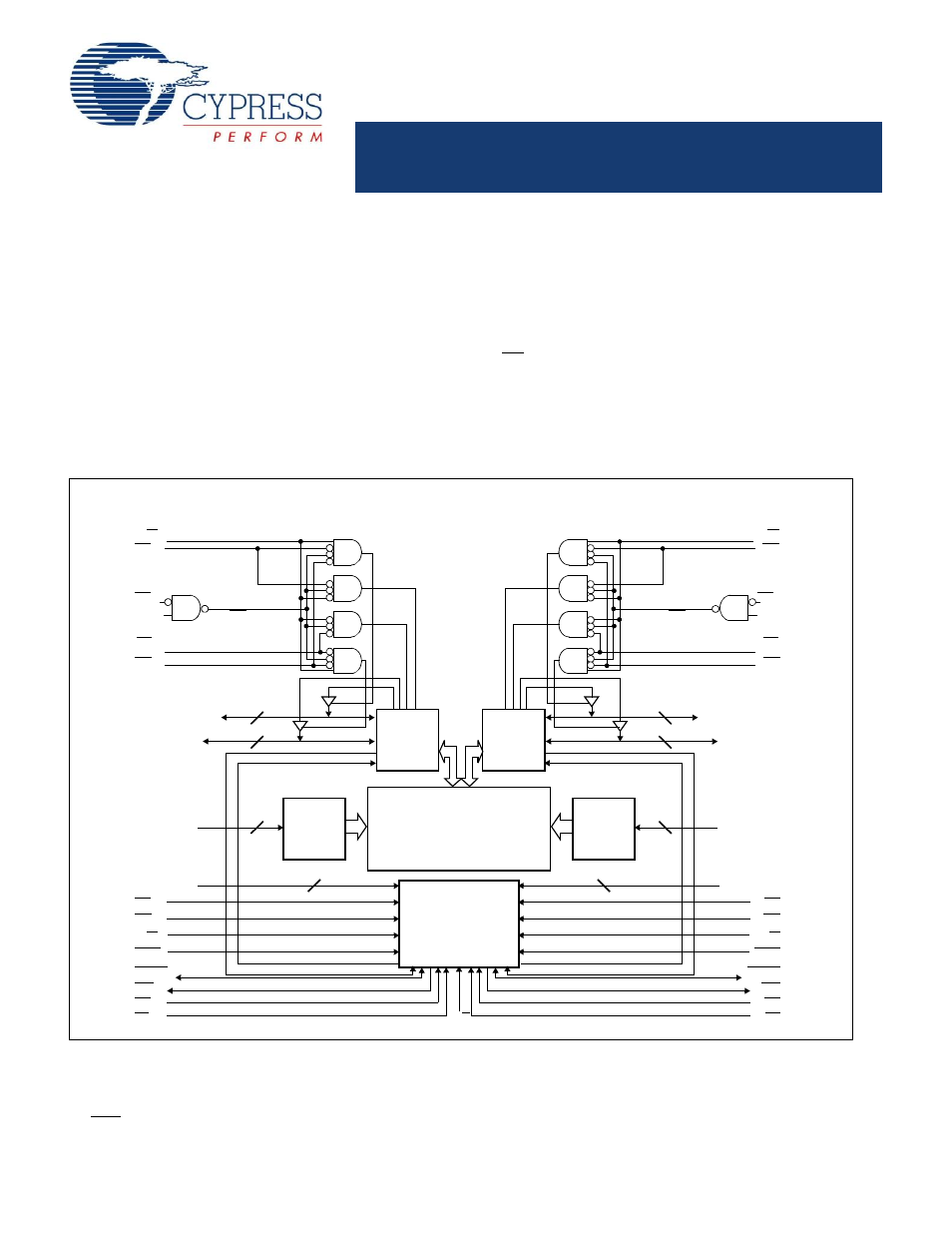

R/W

L

CE

0L

CE

1L

OE

L

I/O

8/9L

–I/O

15/17L

I/O

Control

Address

Decode

A

0L

–A

14/15L

CE

L

OE

L

R/W

L

BUSY

L

I/O

Control

CE

L

Interrupt

Semaphore

Arbitration

SEM

L

INT

L

M/S

UB

L

LB

L

I/O

0L

–I/O

7/8L

R/W

R

CE

0R

CE

1R

OE

R

I/O

8/9L

–I/O

15/17R

CE

R

UB

R

LB

R

I/O

0L

–I/O

7/8R

UB

L

LB

L

Logic Block Diagram

A

0L

–A

14/15L

True Dual-Ported

RAM Array

A

0R

–A

14/15R

CE

R

OE

R

R/W

R

BUSY

R

SEM

R

INT

R

UB

R

LB

R

Address

Decode

A

0R

–A

14/15R

[5]

[6]

[5]

15/16

8/9

8/9

15/16

8/9

8/9

15/16

15/16

Document Outline

- Features

- Logic Block Diagram

- Pin Configurations

- Pin Configurations (continued)

- Selection Guide

- Pin Definitions

- Architecture

- Functional Description

- Maximum Ratings

- Operating Range

- Electrical Characteristics Over the Operating Range

- Capacitance[5]

- Switching Characteristics Over the Operating Range[6]

- Data Retention Mode

- Timing

- Switching Waveforms

- Ordering Information

- Package Diagram

- Document History Page

- Sales, Solutions, and Legal Information