Pll characteristics – Cypress HOTLink II CYV15G0104TRB User Manual

Page 20

CYV15G0104TRB

Document #: 38-02100 Rev. *B

Page 20 of 27

t

TRGH

TRGCLKA HIGH Time (TRGRATEA = 1)(Half Rate)

5.9

ns

TRGCLKA HIGH Time (TRGRATEA = 0)(Full Rate)

2.9

[16]

ns

t

TRGL

TRGCLKA LOW Time (TRGRATEA = 1)(Half Rate)

5.9

ns

TRGCLKA LOW Time (TRGRATEA = 0)(Full Rate)

2.9

[16]

ns

t

TRGD

[23]

TRGCLKA Duty Cycle

30

70

%

t

TRGR

[16, 17, 18]

TRGCLKA Rise Time (20%–80%)

2

ns

t

TRGF

[16, 17, 18]

TRGCLKA Fall Time (20%–80%)

2

ns

t

TRGRX

[24]

TRGCLKA Frequency Referenced to Received Clock Frequency

–0.15

+0.15

%

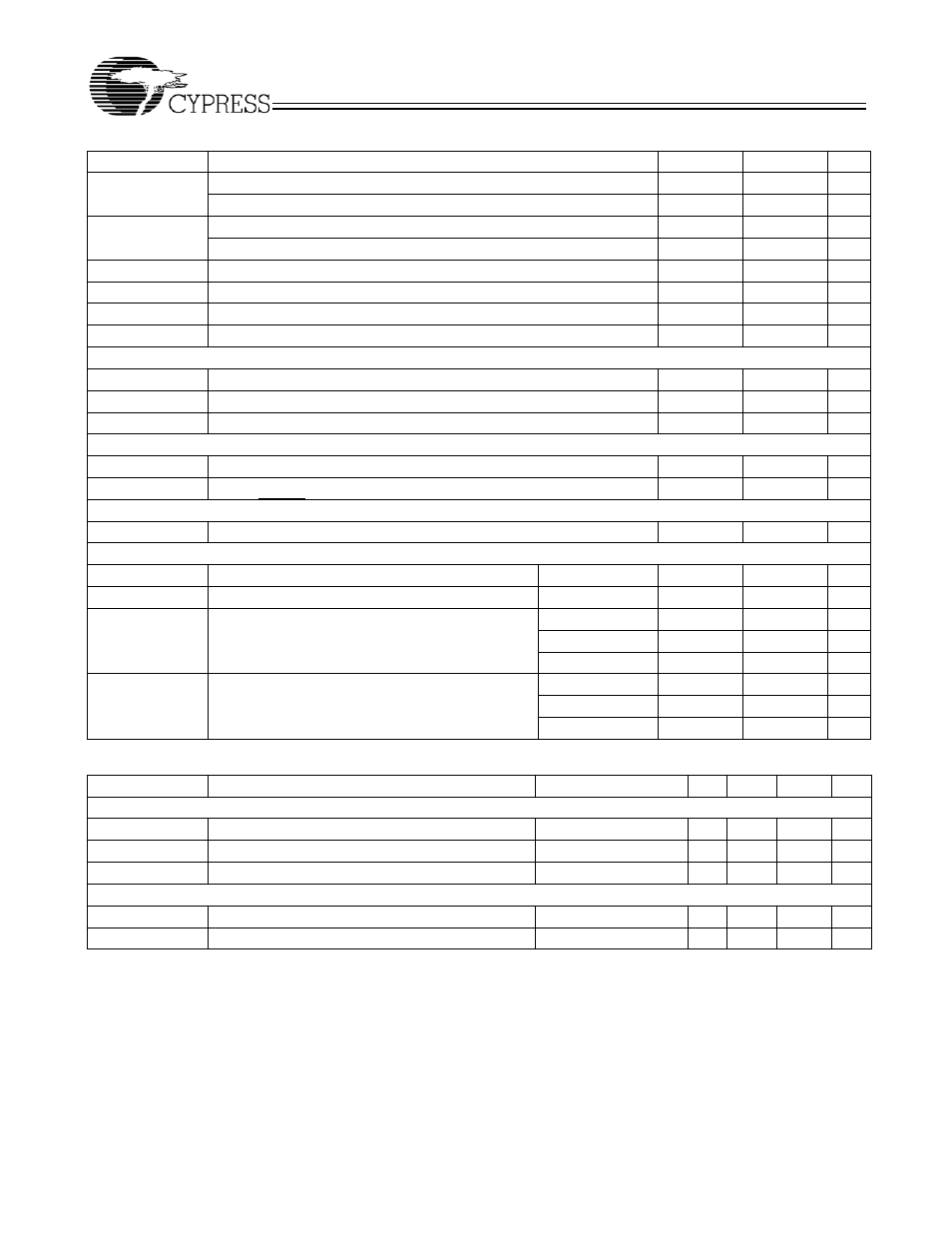

CYV15G0104TRB Bus Configuration Write Timing Characteristics Over the Operating Range

t

DATAH

Bus Configuration Data Hold

0

ns

t

DATAS

Bus Configuration Data Setup

10

ns

t

WRENP

Bus Configuration WREN Pulse Width

10

ns

CYV15G0104TRB JTAG Test Clock Characteristics Over the Operating Range

f

TCLK

JTAG Test Clock Frequency

20

MHz

t

TCLK

JTAG Test Clock Period

50

ns

CYV15G0104TRB Device RESET Characteristics Over the Operating Range

t

RST

Device RESET Pulse Width

30

ns

CYV15G0104TRB Transmitter and Reclocker Serial Output Characteristics Over the Operating Range

Parameter

Description

Condition

Min.

Max.

Unit

t

B

Bit Time

660

5128

ps

t

RISE

[16]

CML Output Rise Time 20

−80% (CML Test Load)

SPDSELx = HIGH

50

270

ps

SPDSELx= MID

100

500

ps

SPDSELx =LOW

180

1000

ps

t

FALL

[16]

CML Output Fall Time 80

−20% (CML Test Load)

SPDSELx = HIGH

50

270

ps

SPDSELx = MID

100

500

ps

SPDSELx =LOW

180

1000

ps

PLL Characteristics

Parameter

Description

Condition

Min.

Typ.

Max.

Unit

CYV15G0104TRB Transmitter Output PLL Characteristics

t

JTGENSD

[16, 25]

Transmit Jitter Generation - SD Data Rate

REFCLKB = 27 MHz

200

ps

t

JTGENHD

[16, 25]

Transmit Jitter Generation - HD Data Rate

REFCLKB = 148.5 MHz

76

ps

t

TXLOCK

Transmit PLL lock to REFCLKB±

200

µs

CYV15G0104TRB Reclocker Output PLL Characteristics

t

JRGENSD

[16, 26]

Reclocker Jitter Generation - SD Data Rate

TRGCLKA = 27 MHz

133

ps

t

JRGENHD

[16, 26]

Reclocker Jitter Generation - HD Data Rate

TRGCLKA = 148.5 MHz

107

ps

Notes:

23. The duty cycle specification is a simultaneous condition with the t

TRGH

and t

TRGL

parameters. This means that at faster character rates the TRGCLKA± duty

cycle cannot be as large as 30%–70%.

24. TRGCLKA± has no phase or frequency relationship with the recovered clock(s) and only acts as a centering reference to reduce clock synchronization time.

TRGCLKA± must be within

±1500 PPM (±0.15%) of the transmitter PLL reference (REFCLK±) frequency. Although transmitting to a HOTLink II receiver channel

necessitates the frequency difference between the transmitter and receiver reference clocks to be within ±1500-PPM, the stability of the crystal needs to be

within the limits specified by the appropriate standard when transmitting to a remote receiver that is compliant to that standard.

25. While sending BIST data at the corresponding data rate, after 10,000 histogram hits, time referenced to REFCLKB± input.

26. Receiver input stream is BIST data from the transmit channel. This data is reclocked and output to a wide-bandwidth digital sampling oscilloscope. The

measurement was recorded after 10,000 histogram hits, time referenced to REFCLKB± of the transmit channel.

CYV15G0104TRB AC Electrical Characteristics

(continued)

Parameter

Description

Min.

Max

Unit