Cypress 256K (32K x 8) CY62256 User Manual

Features, Functional description

256K (32K x 8) Static RAM

CY62256

Cypress Semiconductor Corporation

•

3901 North First Street

•

San Jose

•

CA 95134

•

408-943-2600

Document #: 38-05248 Rev. *B

Revised August 27, 2002

Features

• High speed: 55 ns and 70 ns

• Voltage range: 4.5V–5.5V operation

• Low active power (70 ns, LL version)

— 275 mW (max.)

• Low standby power (70 ns, LL version)

— 28

µ

W (max.)

• Easy memory expansion with CE and OE features

• TTL-compatible inputs and outputs

• Automatic power-down when deselected

• CMOS for optimum speed/power

• Package available in a standard 450-mil-wide (300-mil

body width) 28-lead narrow SOIC, 28-lead TSOP-1,

28-lead reverse TSOP-1, and 600-mil 28-lead PDIP

packages

Functional Description

[1]

The CY62256 is a high-performance CMOS static RAM

organized as 32K words by 8 bits. Easy memory expansion is

provided by an active LOW chip enable (CE) and active LOW

output enable (OE) and three-state drivers. This device has an

automatic power-down feature, reducing the power

consumption by 99.9% when deselected.

An active LOW write enable signal (WE) controls the

writing/reading operation of the memory. When CE and WE

inputs are both LOW, data on the eight data input/output pins

(I/O

0

through I/O

7

) is written into the memory location

addressed by the address present on the address pins (A

0

through A

14

). Reading the device is accomplished by selecting

the device and enabling the outputs, CE and OE active LOW,

while WE remains inactive or HIGH. Under these conditions,

the contents of the location addressed by the information on

address pins are present on the eight data input/output pins.

The input/output pins remain in a high-impedance state unless

the chip is selected, outputs are enabled, and write enable

(WE) is HIGH.

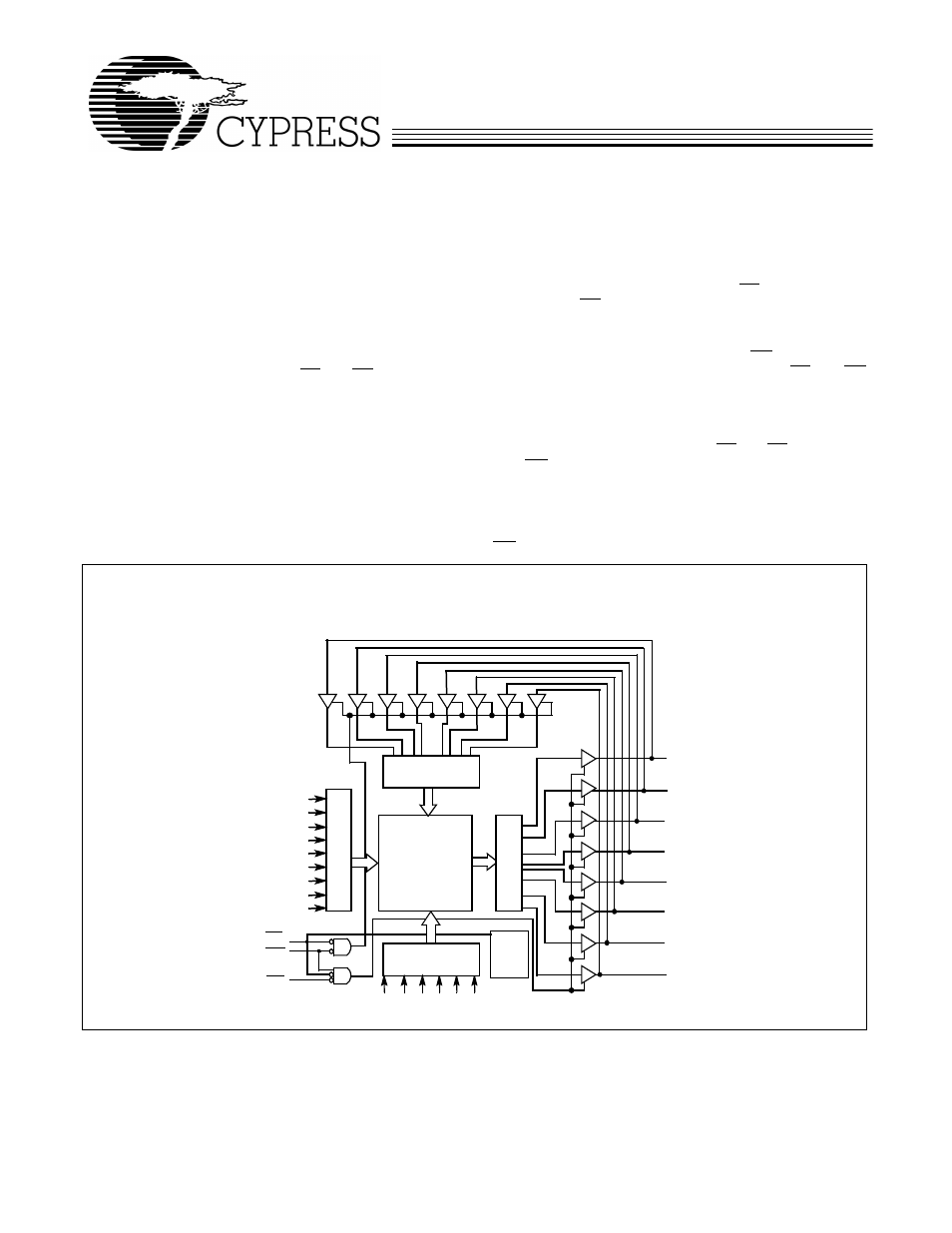

A

9

A

8

A

7

A

6

A

5

A

4

A

3

A

2

COLUMN

DECODER

R

O

W

DE

CODE

R

SEN

SE AM

PS

INPUTBUFFER

POWER

DOWN

WE

OE

I/O

0

CE

I/O

1

I/O

2

I/O

3

512 x 512

ARRAY

I/O

7

I/O

6

I/O

5

I/O

4

A

10

A

13

A

11

A

12

A

A

14

A

1

0

Logic Block Diagram

Note:

1.

For best practice recommendations, please refer to the Cypress application note “System Design Guidelines” on http://www.cypress.com.