Kontron PB-TIM2 User Manual

Page 13

PB-TIM2 User’s Manual

Chapter 2 Functional Description

2.2 Board Operation

After power-up, all outputs are passive and all registers are cleared including the interrupt registers. Prescalers are set to

divide by one and the counters are disabled. Input (A) operates as a trigger responding to a rising edge signal, input (B)

operates as a gate that enables the counters when a voltage is applied, input (C) is initialized as a timer clear and the

common clear signal is disabled on all three timers.

Under normal operation, the timers are able to be read transparently with continuous comparisons being made between the

current timer value and zero or a preset value. The timer outputs may be activated if the comparison shows a non-zero

value or may be toggled when the timer passes through zero. The timers may be reloaded with a preset value through the

use of the (A) input; timer operation may be blocked by using the (B) or gate input while the counter(s) may be reset

using the local (C) clear input or common clear.

The software allows the prescaler value(s) to be set; enables or clears the timer(s); defines the edge selection on the trigger

input (A) and whether the (B) gate input is edge or level sensitive. In addition, it gives interrupt authorization on

comparison; zero detect; input (A) or (B) and identifies/clears pending interrupts and configures the timer as a ring

counter; sets the counter direction (up or down) and defines when or from which source the timer should be reloaded.

When accessing the board registers, the piggyback will generate a DTACK on each memory location; reading a location

that is not registered in the address map will produce irrelevant data ($FF). Timer and comparator values are 16-bit and

may be accessed as either 3 consecutive bytes or as 2 consecutive words.

Upon initialization, the process should verify the board’s hardware and software IDs.

2.3 Timer Operating Modes

Table 2.3.1 summarizes the timer possibilities indicating the input and output functions, the interrupt possibilities, the

measurement results and the timer modes.

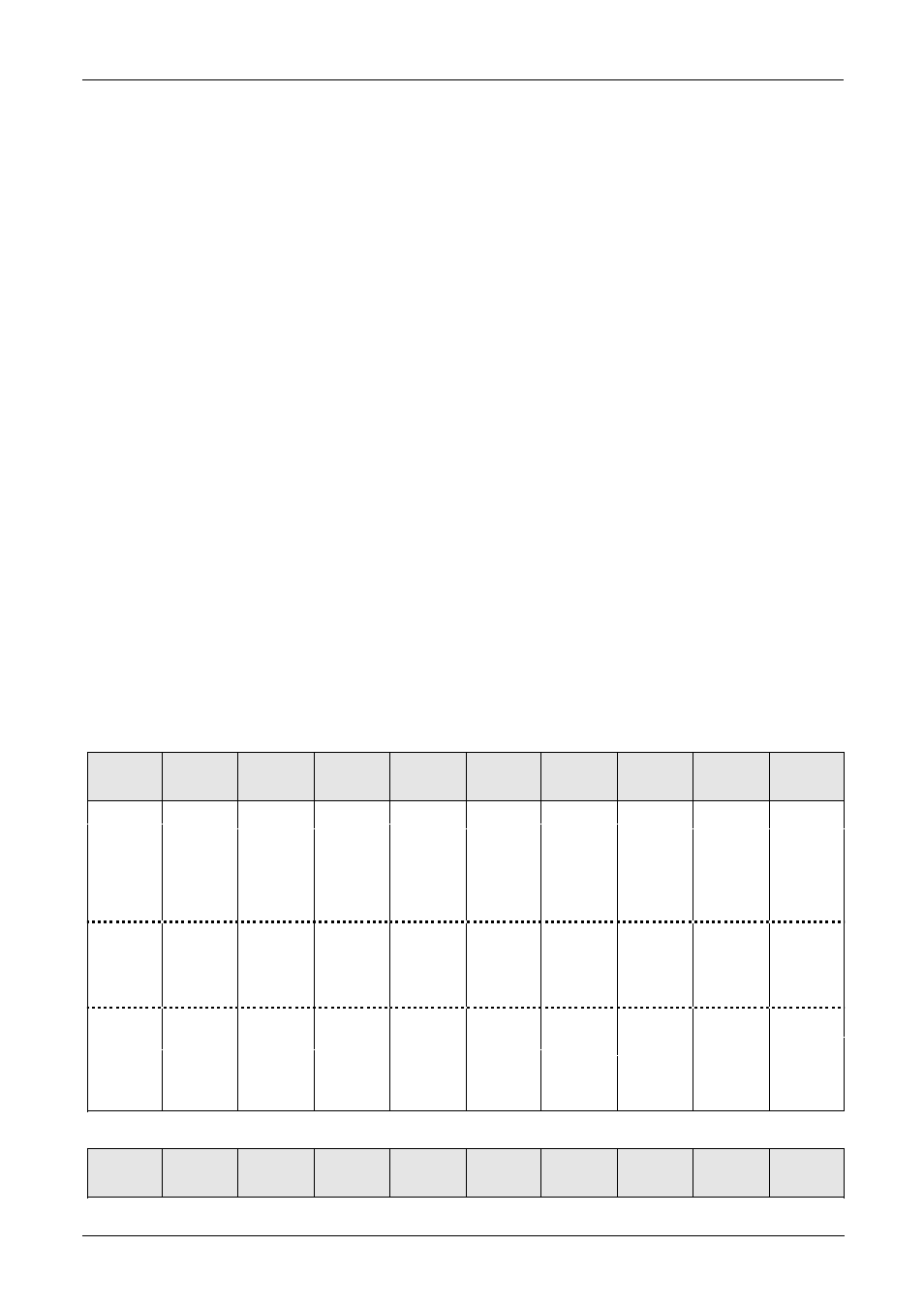

Table 2.3.1 Timer Characteristics

Mode

Timer

Compare

Register

Software

Control

A

B

C

Output

IRQ

Result

Hard

single

shot

Count-

down

stop at 0/

load on

A

Period

Load on

edge

Clear

counter/

output

Passive

if 0

On 0

Soft

single

shot

Count-

down

stop at 0

Software

load

Clear

counter/

output

Passive

if 0

On 0

Tick

Count-

down

load at 0

Period

Enable

counting

Ring

counting

Clear

counter/

output/

Ring

mode

Passive

if 0

On 0

Mode

Timter

Compare

Register

Software

Control

A

B

C

Output

IRQ

Result

July 30, 1997

© 1996 PEP Modular Computers

Page 2-3