Snapshot overview – Achronix Speedster22i Snapshot User Manual

Page 4

Snapshot Overview

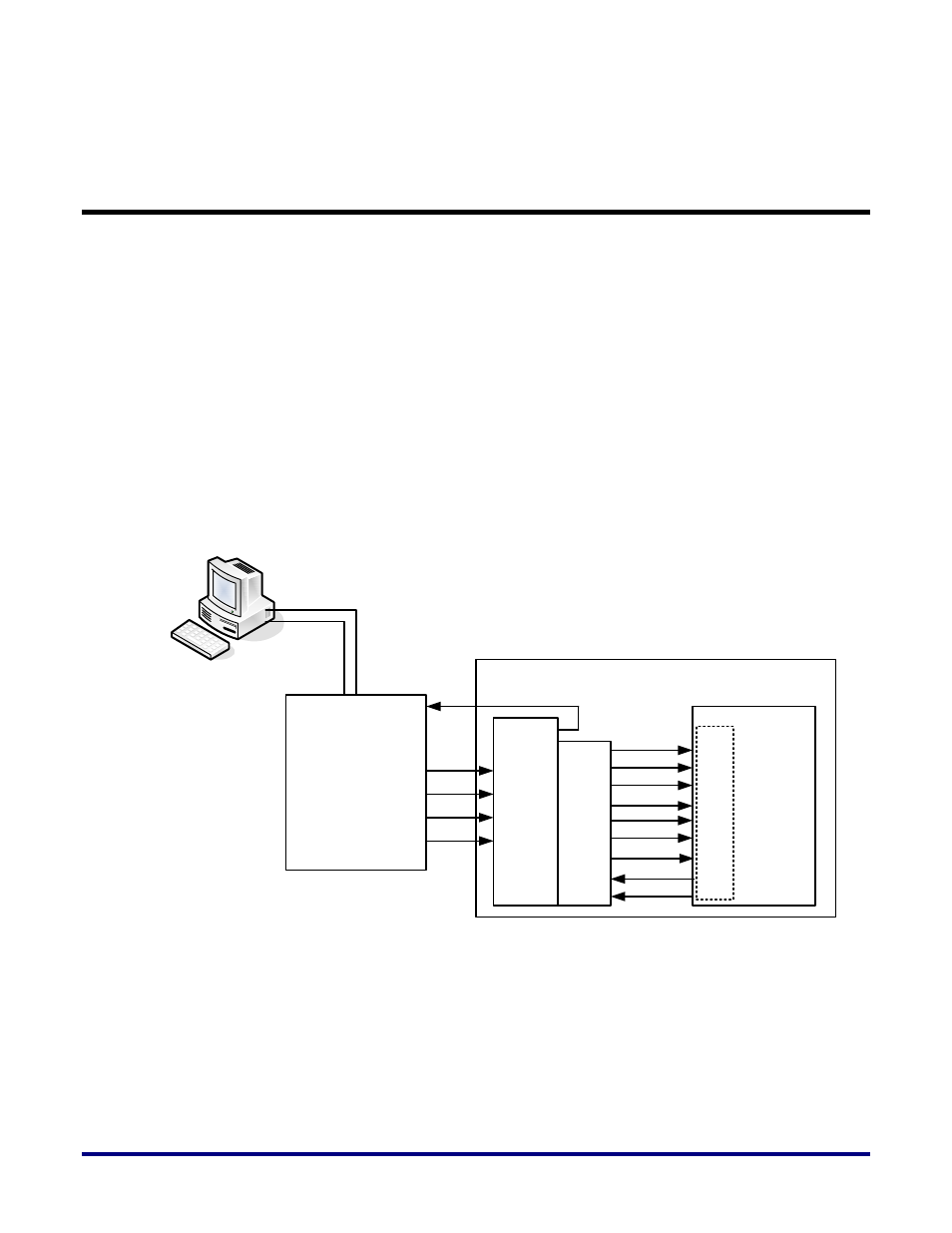

Snapshot is the real-time design debugging tool for Speedster22iHD FPGAs. Snapshot,

which is embedded in the ACE Software, delivers a practical platform to evaluate the signals

of a user’s design in real-time. To run the Snapshot debugger tool, the Snapshot macro needs

to be instantiated inside the RTL. After instantiating the macro and programming the device,

the user will be able to debug the design through the ACE Snapshot Debugger GUI.

The Snapshot macro, when instantiated in the design, can be used to interface with any logic

mapped to the FPGA core. The Snapshot macro provides a JTAG interface at the FPGA pins

to observe debug logic mapped in the core. Through the Snapshot macro and GUI, the user is

able to customize what, when and how much observation will be done by specifying the

nodes, trigger points and pre-store lengths.

Figure 1 shows a block diagram overview of the different components in the Snapshot

debugging tool and its connection to the Speedster22iHD FPGA device.

`

BitPorter

TDI

TMS

TCK

TRSTN

TDO

Speedster22iHD

JTAP

Macro

JTAG

TAP

CNTRL

tck

capture

shift

update

trstn

usr1_sel

usr2_sel

usr1_tdr_in

usr2_tdr_in

S

N

A

P

S

H

O

T

C

O

R

E

User Logic

Figure 1: Snapshot Overview

4

UG016, September 22, 2014