Sram read cycles #1 and #2, Stk14ca8 – Cypress AutoStore STK14CA8 User Manual

Page 5

STK14CA8

Document Number: 001-51592 Rev. **

Page 5 of 16

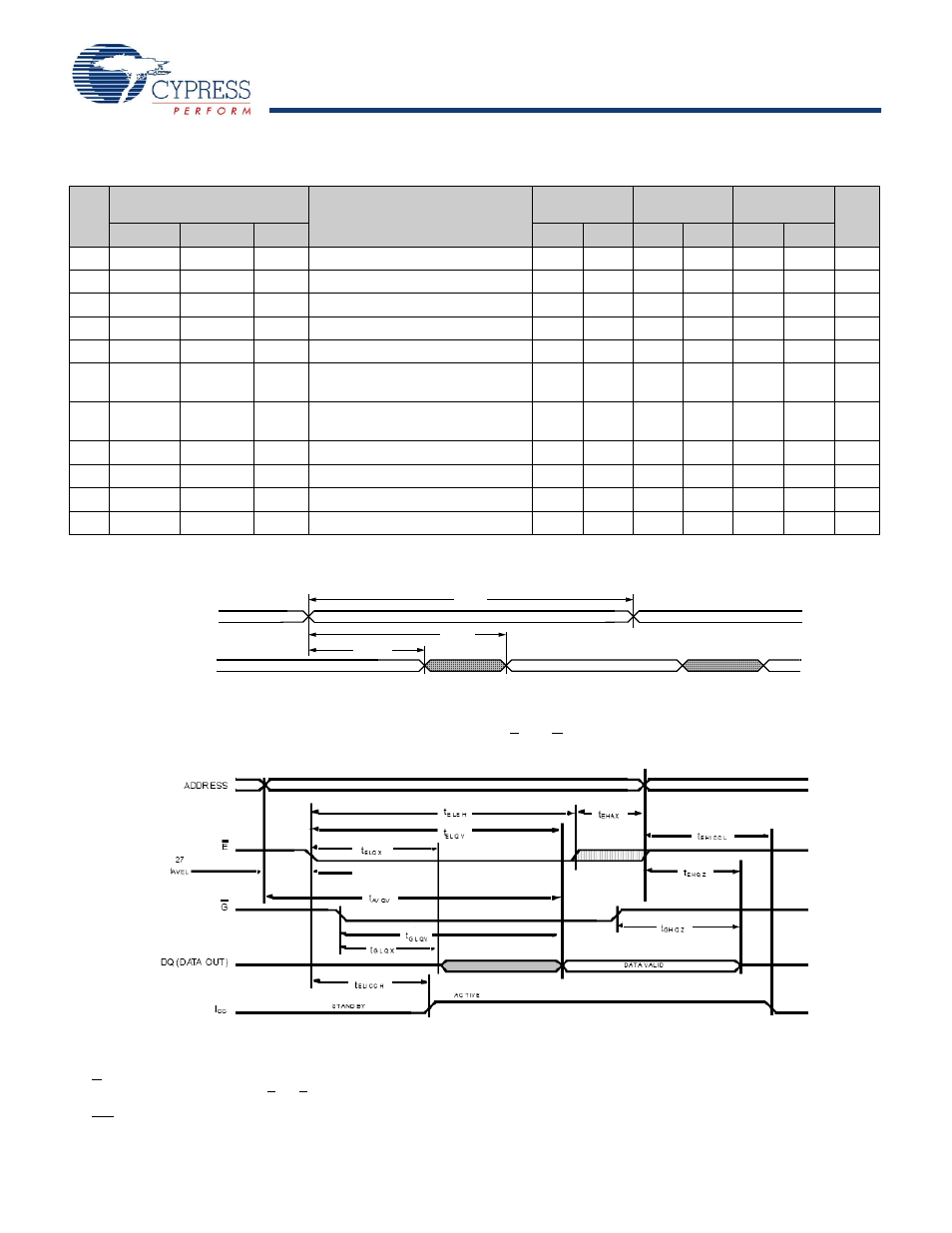

SRAM READ Cycles #1 and #2

Figure 6. SRAM READ Cycle #1: Address Controlled

Figure 7. SRAM READ Cycle #2: E and G Controlled

NO.

Symbols

Parameter

STK14CA8-25 STK14CA8-35 STK14CA8-45

Units

#1

#2

Alt.

Min

Max

Min

Max

Min

Max

1

t

ELQV

t

ACS

Chip Enable Access Time

25

35

45

ns

2

t

AVAV

t

ELEH

[3]

t

RC

Read Cycle Time

25

35

45

ns

3

t

AVQV

t

AVQV

[4]

t

AA

Address Access Time

25

35

45

ns

4

t

GLQV

t

OE

Output Enable to Data Valid

12

15

20

ns

5

t

AXQX

t

AXQX

[4]

t

OH

Output Hold after Address Change

3

3

3

ns

6

t

ELQX

t

LZ

Address Change or Chip Enable to

Output Active

3

3

3

ns

7

t

EHQZ

[5]

t

HZ

Address Change or Chip Disable to

Output Inactive

10

13

15

ns

8

t

GLQX

t

OLZ

Output Enable to Output Active

0

0

0

ns

9

t

GHQZ

t

OHZ

Output Disable to Output Inactive

10

13

15

ns

10

t

ELICCH

[2]

t

PA

Chip Enable to Power Active

0

0

0

ns

11

t

EHICCL

[2]

t

PS

Chip Disable to Power Standby

25

35

45

ns

DATA VALID

t

AXQX

t

AVQV

DQ (DATA OUT)

ADDRESS

t

AVAV

Notes

3. W must be high during SRAM READ cycles.

4. Device is continuously selected with E and G both low

5. Measured

± 200mV from steady state output voltage.

6. HSB must remain high during READ and WRITE cycles