Switching waveforms, Hardware store cycle – Cypress CY14B256L User Manual

Page 13

CY14B256L

Document Number: 001-06422 Rev. *H

Page 13 of 18

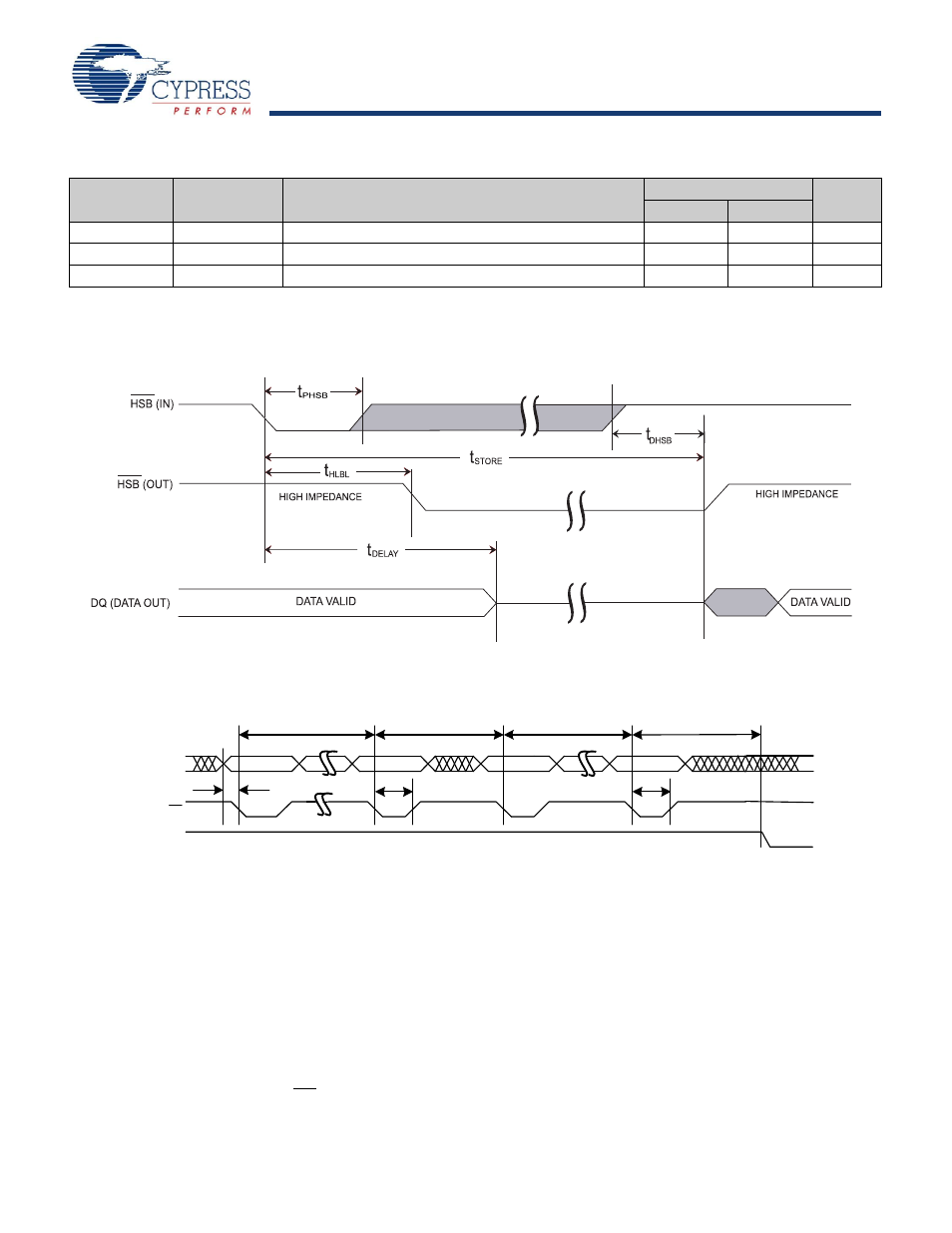

Hardware STORE Cycle

Parameter

Alt

Description

CY14B256L

Unit

Min

Max

t

PHSB

t

HLHX

Hardware STORE Pulse Width

15

ns

t

DELAY

t

HLQZ ,

t

BLQZ

Time Allowed to Complete SRAM Cycle

1

70

μs

t

ss

Soft Sequence Processing Time

70

us

Switching Waveforms

Figure 12. Hardware STORE Cycle

Figure 13. Soft Sequence Processing

$GGUHVV

$GGUHVV

$GGUHVV

$GGUHVV

6RIW6HTXHQFH

&RPPDQG

W

66

W

66

&(

$GGUHVV

9

&&

W

6$

W

&:

6RIW6HTXHQFH

&RPPDQG

W

&:

Notes

17. Read and Write cycles in progress before HSB are given this amount of time to complete.

18. This is the amount of time it takes to take action on a soft sequence command. Vcc power must remain HIGH to effectively register command.

19. Commands such as STORE and RECALL lock out IO until operation is complete which further increases this time. See specific command.

- CY7C1410AV18 (29 pages)

- CY7C1411JV18 (28 pages)

- CY7C1383FV25 (28 pages)

- CY7C1307BV25 (21 pages)

- CY7C1041DV33 (13 pages)

- CY62167EV18 (13 pages)

- Perform CY7C1565V18 (28 pages)

- STK11C68-5 (15 pages)

- 7C185-20 (11 pages)

- CY7C1168V18 (27 pages)

- CY7C1318CV18-250BZC (26 pages)

- CY7C1364C (18 pages)

- Perform CY7C1382D (34 pages)

- CY7C106D (11 pages)

- CY14E102N (21 pages)

- CY7C1418AV18 (31 pages)

- enCoRe CY7C638xx (83 pages)

- CY7C1018DV33 (9 pages)

- CY7C1292DV18 (23 pages)

- CY7C130 (19 pages)

- CY7C1424BV18 (30 pages)

- CY62157EV18 (12 pages)

- CY7C1392BV18 (31 pages)

- CY7C1302DV25 (18 pages)

- Perform CY7C1511KV18 (31 pages)

- West Bridge Astoria AN46860 (4 pages)

- CY7C1386FV25 (30 pages)

- CY7C1163V18 (29 pages)

- CY7C1266V18 (27 pages)

- CY7C1334H (13 pages)

- CY7C1018CV33 (7 pages)

- CY62136VN (12 pages)

- AN20639 (3 pages)

- CY7C1338G (17 pages)

- CY7C1462AV33 (27 pages)

- CY7C1145V18 (28 pages)

- STK11C88 (15 pages)

- CY7C1231H (12 pages)

- Perform CY7C142 (15 pages)

- CY14E256L (18 pages)

- STK15C88 (15 pages)

- CY7C1297H (15 pages)

- CY7C1441AV33 (31 pages)

- CapSense CY8C20x36 (34 pages)