Cypress CY14B256K User Manual

Page 27

CY14B256K

Document Number: 001-06431 Rev. *H

Page 27 of 28

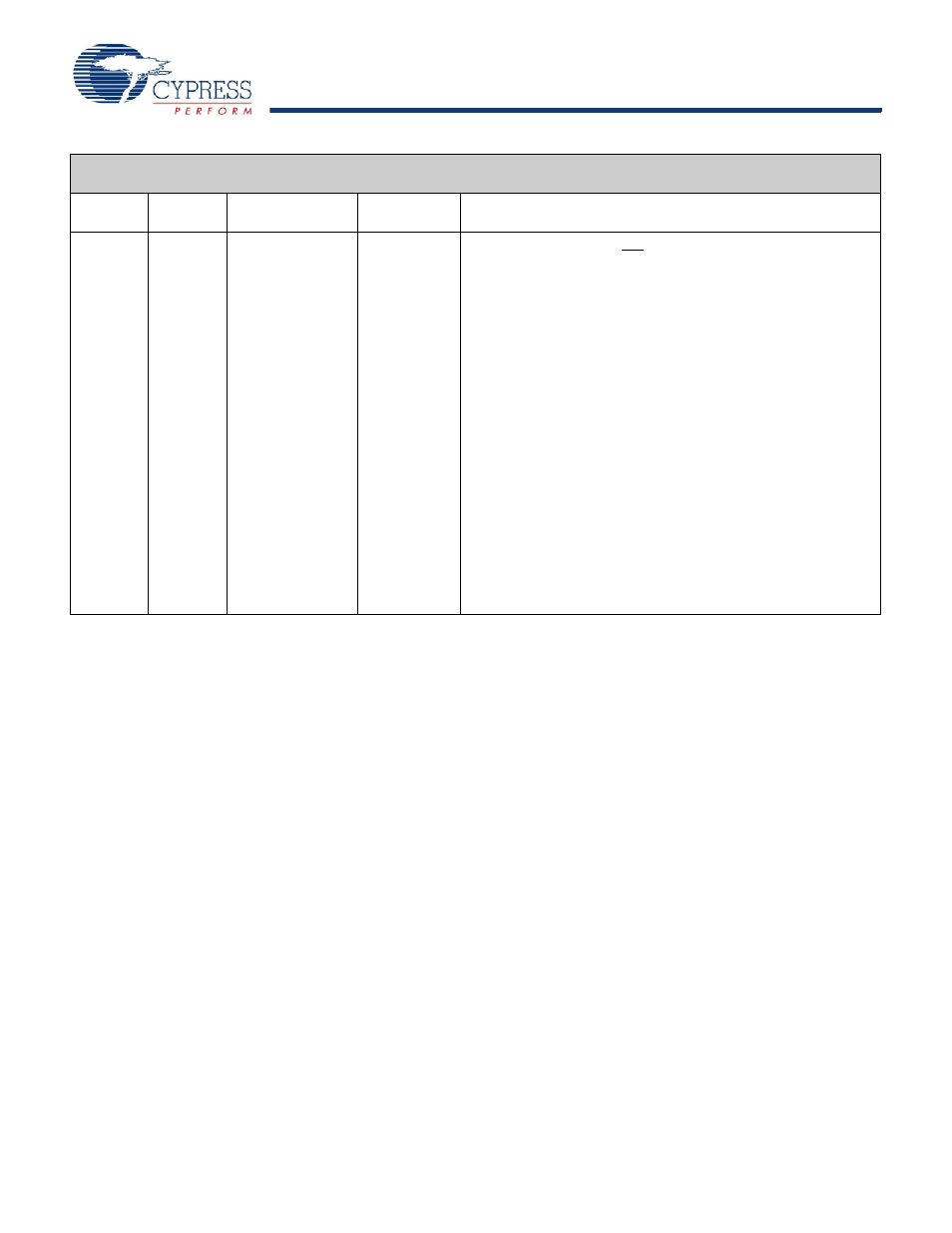

*H

2663934

GVCH/PYRS

02/24/09

Updated Features section

Updated pin definition of WE pin

Updated “Reading the clock”, “Backup Power”, “Stopping and

starting the Oscillator” and “Alarm” descriptions under RTC

operation

Modified “Figure 4. RTC Recommended Component Configuration”

Added footnote 4

Added footnote 6

Added default values to RTC Register Map” table

Updated flag register description in Register Map Detail” table

Added Industrial specs for 25ns and 35ns speed

Changed V

IH

from vcc+0.3 to Vcc+0.5

Added “Data Retention and Endurance” table on page 15

Added thermal resistance values

Added alternate parameters in the AC switching characteristics

table

Renamed t

OH

to t

OHA

Changed t

HRECALL

from 20 to 40ms

Changed t

RECALL

spec from 100

μs to 170μs (Including t

ss

of 70us)

Renamed t

AS

to t

SA

Renamed t

GHAX

to t

HA

Renamed t

HLHX

to t

PHSB

Updated Figure 16

Added truth table for SRAM operations

Document Title: CY14B256K 256 Kbit (32K x 8) nvSRAM with Real Time Clock

Document Number: 001-06431

Rev.

ECN

Orig. of Change

Submission

Date

Description of Change