Ac switching characteristics (continued), Ac switching characteristics – Cypress CY14B256K User Manual

Page 18

CY14B256K

Document Number: 001-06431 Rev. *H

Page 18 of 28

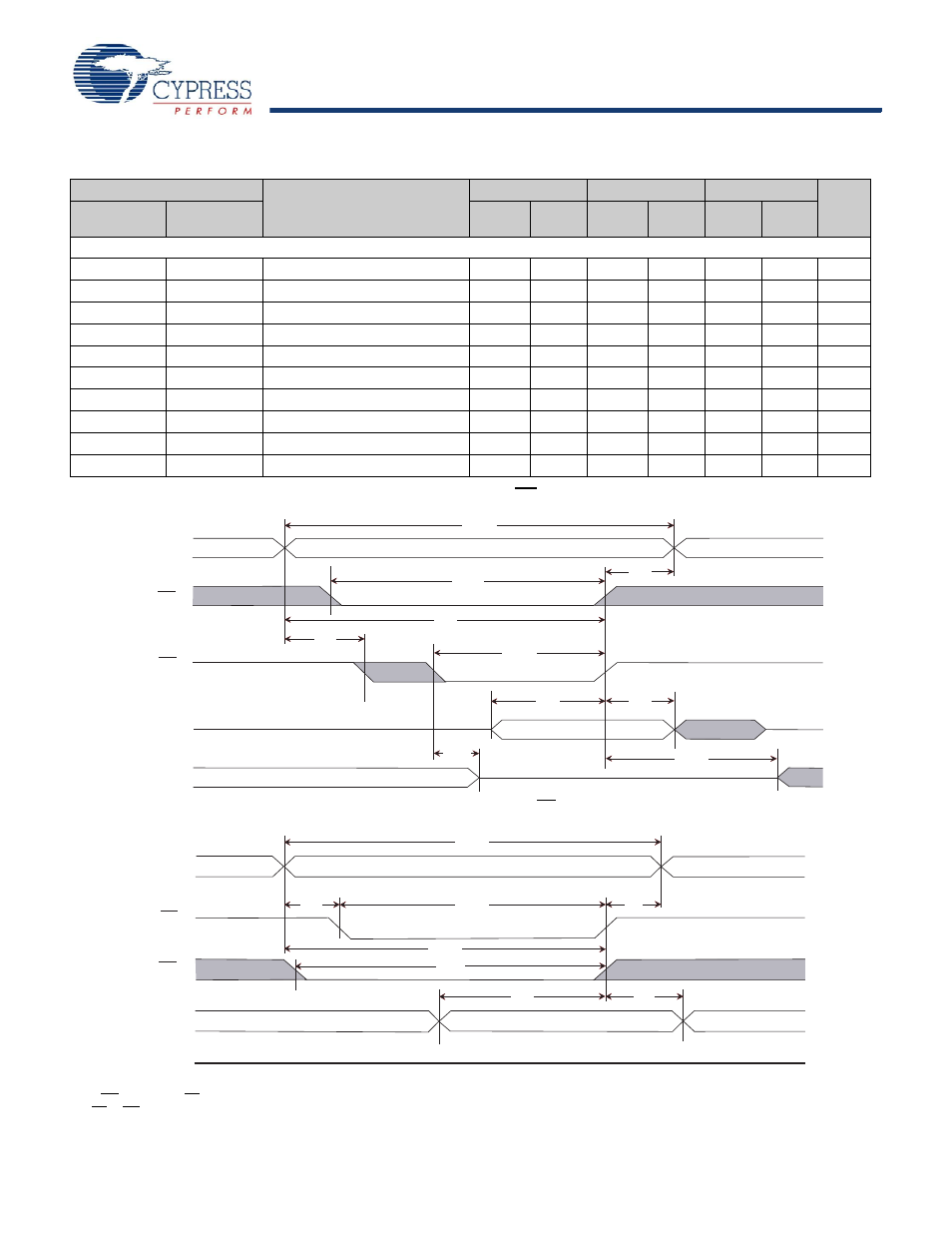

AC Switching Characteristics

(continued)

Parameter

Description

25 ns

35 ns

45 ns

Unit

Min

Max

Min

Max

Min

Max

Cypress

Parameter

Alt.

Parameter

SRAM Write Cycle

t

WC

t

AVAV

Write Cycle Time

25

35

45

ns

t

PWE

t

WLWH,

t

WLEH

Write Pulse Width

20

25

30

ns

t

SCE

t

ELWH,

t

ELEH

Chip Enable To End of Write

20

25

30

ns

t

SD

t

DVWH,

t

DVEH

Data Setup to End of Write

10

12

15

ns

t

HD

t

WHDX,

t

EHDX

Data Hold After End of Write

0

0

0

ns

t

AW

t

AVWH,

t

AVEH

Address Setup to End of Write

20

25

30

ns

t

SA

t

AVWL,

t

AVEL

Address Setup to Start of Write

0

0

0

ns

t

HA

t

WHAX,

t

EHAX

Address Hold After End of Write

0

0

0

ns

t

HZWE

t

WLQZ

Write Enable to Output Disable

10

13

15

ns

t

LZWE

t

WHQX

Output Active After End of Write

3

3

3

ns

Figure 10. SRAM Write Cycle 1: WE Controlled

Figure 11. SRAM Write Cycle 2: CE Controlled

t

WC

t

SCE

t

HA

t

AW

t

SA

t

PWE

t

SD

t

HD

t

HZWE

t

LZWE

ADDRESS

CE

WE

DATA IN

DATA OUT

DATA VALID

HIGH IMPEDANCE

PREVIOUS DATA

t

WC

ADDRESS

t

SA

t

SCE

t

HA

t

AW

t

PWE

t

SD

t

HD

CE

WE

DATA IN

DATA OUT

HIGH IMPEDANCE

DATA VALID

Notes

15. If WE is Low when CE goes Low, the outputs remain in the High Impedance State.

16. CE or WE are greater than V

IH

during address transitions.