Rockwell Automation 61C345 4 Input 4-20mA Analog Rail Module User Manual

Page 29

4Ć7

4.1.2

AutoMate Programming in Rail Mode

In Rail mode, the Analog Rail module is imaged in one I/O register of

the processor. Data from one of the four channels will occupy the

register as a function of the channel select bits. The active channel

is updated at the end of each scan. For the input channels, the two

channel select bits in the register must be set to the appropriate

input channel number. After the I/O update, the register contains the

data in the format shown in figure 4.7.

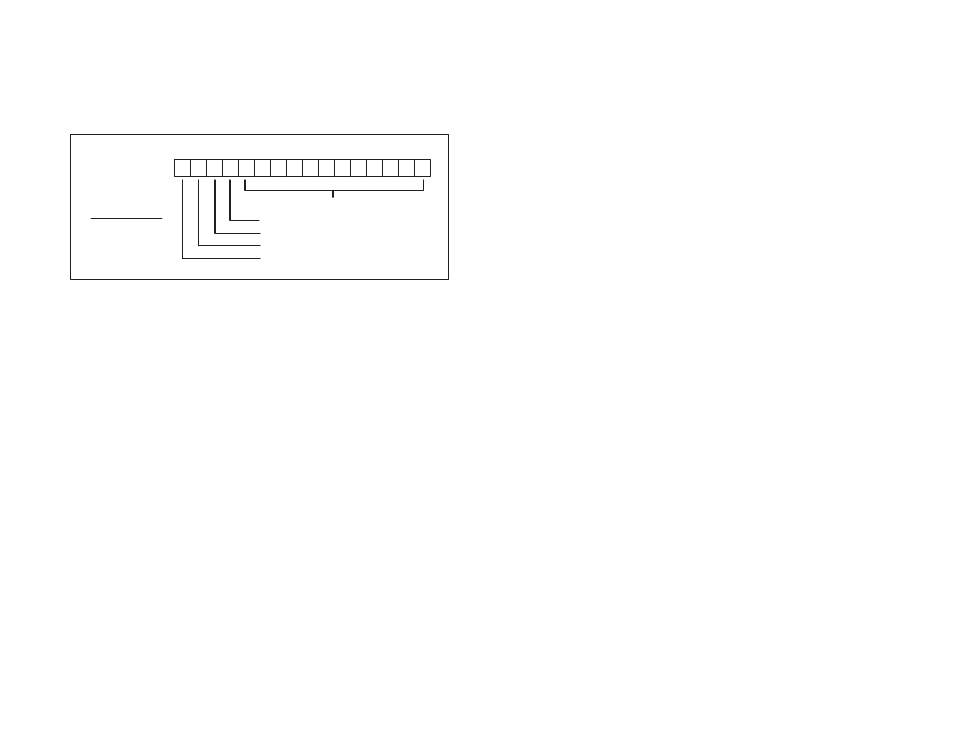

17 16 15 14 13 12 11 10 7 6 5 4 3 2 1 0

Octal

12 bits of converted analog data

overĆrange (1=overĆrange)

underĆrange (1=underĆrange)

channel being read: LSB

channel being read: MSB

MSB

0

0

1

1

LSB

0 =

1 =

0 =

1 =

CH#

CH 0

CH 1

CH 2

CH 3

Figure 4.7 Ć Rail Mode Register Image for Input Channels

The Analog Rail module data may also be accessed in the middle of

the scan (as opposed to the end of the scan, which is the normal

mode of operation for digital rail I/O) using the appropriate number

of Analog In (AIN) blocks. The AIN block will check whether the

overĆrange or underĆrange bits have been set by the module and the

error coil will be energized, if applicable. See section 4.1.4 for more

information about the AIN block.

Note that the AIN block is supported by the AutoMate 20E

M/N 45C224 and 45C225, but not the AutoMate 20 (M/N 45C20,

45C21, 45C220, 45C221) by APX Version 3.0.

For processors that do not support the AIN block, you can use the

MOVE block to move data in and out of the registers assigned and

to determine the channel select bits. OverĆrange and underĆrange

bits should be used as inputs to error coils. The I/O update will

occur automatically at the end of each scan. See Appendix C for a

sample AutoMate program that reads from the Analog Rail module

without using AIN blocks.

4.1.3

AutoMate Programming in Local Head Mode

In Local Head mode, the module is imaged in four I/O registers of

the processor. Data from all four channels is always available and

will be updated at the end of each scan. It is not necessary to select

the channel. After the I/O update, the register contains the data in

the format shown in figure 4.8.