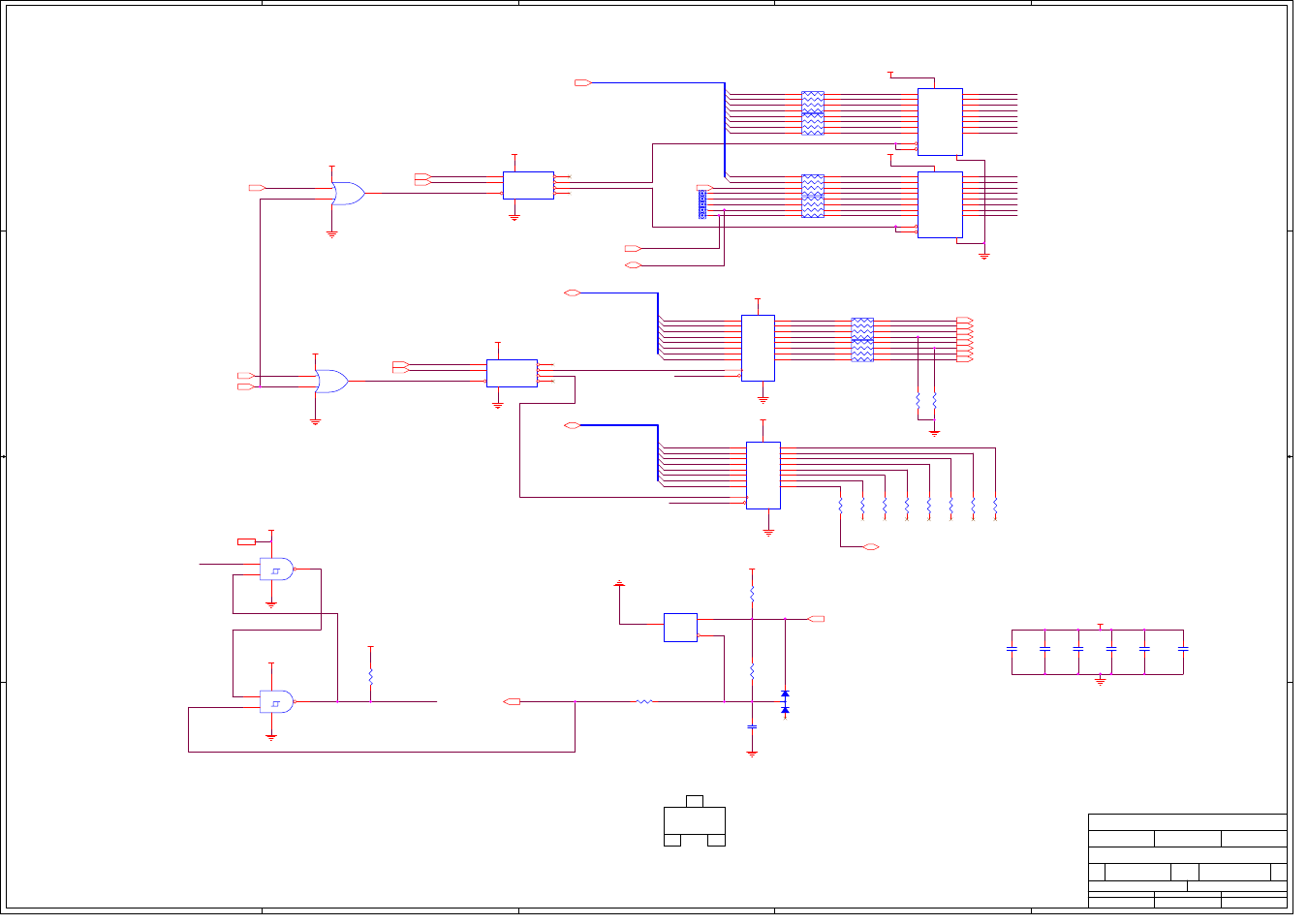

Benq corporation, Sot23, Generate harward reset singnal – BenQ DLP PROJECTOR PE8700 User Manual

Page 77

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

CP U_D1

CP U_D7

CP U_D4

CP U_D0

CP U_D5

CP U_D6

CPU_ D[0..7]

OUT_BUFFER_OE_N

CP U_D3

CP U_D2

OUTLTCH1_1

OUTLTCH1_2

OUTLTCH1_3

OUTLTCH1_4

OUTLTCH1_5

OUTLTCH1_6

OUTLTCH1_7

OUTLTCH1_8

RESET_N

S_B UFFER

OUT_BUFFER_OE_N

IOCS_WR_SET_N

3.3VRESET

CPU _WR_N

CPU_A2

CPU_A1

IOCS_WR_SET_N

INLTCH1_8

K EYPAD6

K EYPAD9

INLTCH1_2

CP U_D0

CP U_D4

CP U_D3

CP U_D5

K EYPAD8

CP U_D1

INLTCH2_4

INLTCH1_7

CP U_D0

K EYPAD2

K EYPAD0

INLTCH1_4

CP U_D3

CP U_D7

INLTCH2_3

K EYPAD5

INLTCH1_6

K EYPAD3

K EYPAD4

IOR D0_N

INLTCH2_2

CP U_D6

CP U_D7

INLTCH1_5

CP U_D1

CP U_D5

INLTCH2_1

K EYPAD7

K EYPAD1

CP U_D2

INLTCH1_1

CP U_D6

CP U_D2

CP U_D4

INLTCH1_3

IOR D1_N

CPU_PCS0_N

CPU_A3

IOR D1_N

IOCS_RD_SET_N

IOR D0_N

CPU_A4

CPU_PCS0_N

INLTCH2_5

INLTCH2_6

INLTCH2_7

INLTCH2_8

WIRE_TP46

WIRE_TP47

DLP_SPARE

I OWR0_N

I OWR0_N

WIRE_TP53

WIRE_TP52

WIRE_TP51

RESETVCC

OUTSPARE1

OUTSPARE2

OUTSPARE3

OUTSPARE4

OUTSPARE5

OUTSPARE6

OUTSPARE7

OUTSPARE8

CP U_D0

CP U_D1

CP U_D2

CP U_D3

CP U_D4

CP U_D5

CP U_D6

CP U_D7

CPU_ D[0..7]

IOWR0_N1

OUT_BUFFER_OE_N

POWERON

RM1_RST_N

CPU_D[0..7]

WRITE_PROT

SII141_PDO

MUX_SEL

MCURESET

+3VS

RESET_N

CPU_A1

CPU_A2

CPU_PCS0_N

CPU_WR_N

TRIGGER

RESETVCC

CPU_A3

CPU_A4

KEY PAD[0..9]

CPU_RD_N

LAMP_PROTECT

DLP_SPARE

CPU_D[0..7]

DVI_SCDT

SPAREO

SPAREI

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

Title

Size

Document Number

R e v .

Date:

Sheet

o f

Project Code

Reviewed By

Approved By

Prepared By

Model Name

PCB P/N

P CB Rev.

Benq Corporation

OEM/ODM Model Name

99.J5877.R22-C3-304-001

MAIN BOARD

8

10

COLIN CHANG

BEN CHEN

48.J5801.S02

S02

ANGEL HU

HT720G

99.J5877.001

0

Thursday, January 16, 2003

NA

Note: All outputs are disabled

after power-up until

IOCS_WR_SET_N is activated by

software.

** Generate Harward RESET Singnal **

1

2

3

RST

GND

VDD

SOT23

AME8500AF27

C90

0.1UF

U7D

74VHC32

12

13

11

14

7

R118

100K

R76

10K

TP52

E1

1

R113

0

D3

BAV99

1

3

2

R78

5.1K

R109

0

RP22 47_RP

1

2

3

4

5

6

7

8

C89

0.1UF

C88

1 U Z

U8C

74HC132

9

10

8

14

7

TP47

E1

1

TP51

E1

1

TP53

E1

1

RP20 47_RP

1

2

3

4

5

6

7

8

U14B

74VHC139

A

14

B

13

G

15

Y0

12

Y1

11

Y2

10

Y3

9

VCC

16

GND

8

RP21 47_RP

1

2

3

4

5

6

7

8

U17

74ABT574

D1

2

D2

3

D3

4

D4

5

D5

6

D6

7

D7

8

D8

9

CLK

11

OC

1

Q1

19

Q2

18

Q3

17

Q4

16

Q5

15

Q6

14

Q7

13

Q8

12

VCC

20

GND

10

R110

0

RP24

47_RP

1

2

3

4

5

6

7

8

U8B

74HC132

4

5

6

14

7

R106

0

TP46

E1

1

R80

1K

U14A

74VHC139

A

2

B

3

G

1

Y0

4

Y1

5

Y2

6

Y3

7

VCC

16

GND

8

C91

0.1UF

U18

AME8500BEET

GND

2

VDD

3

RES

1

U22

74ABT574

D1

2

D2

3

D3

4

D4

5

D5

6

D6

7

D7

8

D8

9

CLK

11

OC

1

Q1

19

Q2

18

Q3

17

Q4

16

Q5

15

Q6

14

Q7

13

Q8

12

VCC

20

GND

10

R77

180

R111

0

RP23

47_RP

1

2

3

4

5

6

7

8

U7A

74VHC32

1

2

3

14

7

R107

0

R75

10K

C92

0.1UF

RP25

47_RP

1

2

3

4

5

6

7

8

C93

0.1UF

C94

0.1UF

U13

74AHC244

1A1

2

1A2

4

1A3

6

1A4

8

2A1

11

2A2

13

2A3

15

2A4

17

1G

1

2G

19

1Y1

18

1Y2

16

1Y3

14

1Y4

12

2Y1

9

2Y2

7

2Y3

5

2Y4

3

VCC

20

GND

10

R112

0

U15

74AHC244

1A1

2

1A2

4

1A3

6

1A4

8

2A1

11

2A2

13

2A3

15

2A4

17

1G

1

2G

19

1Y1

18

1Y2

16

1Y3

14

1Y4

12

2Y1

9

2Y2

7

2Y3

5

2Y4

3

VCC

20

GND

10

R108

0