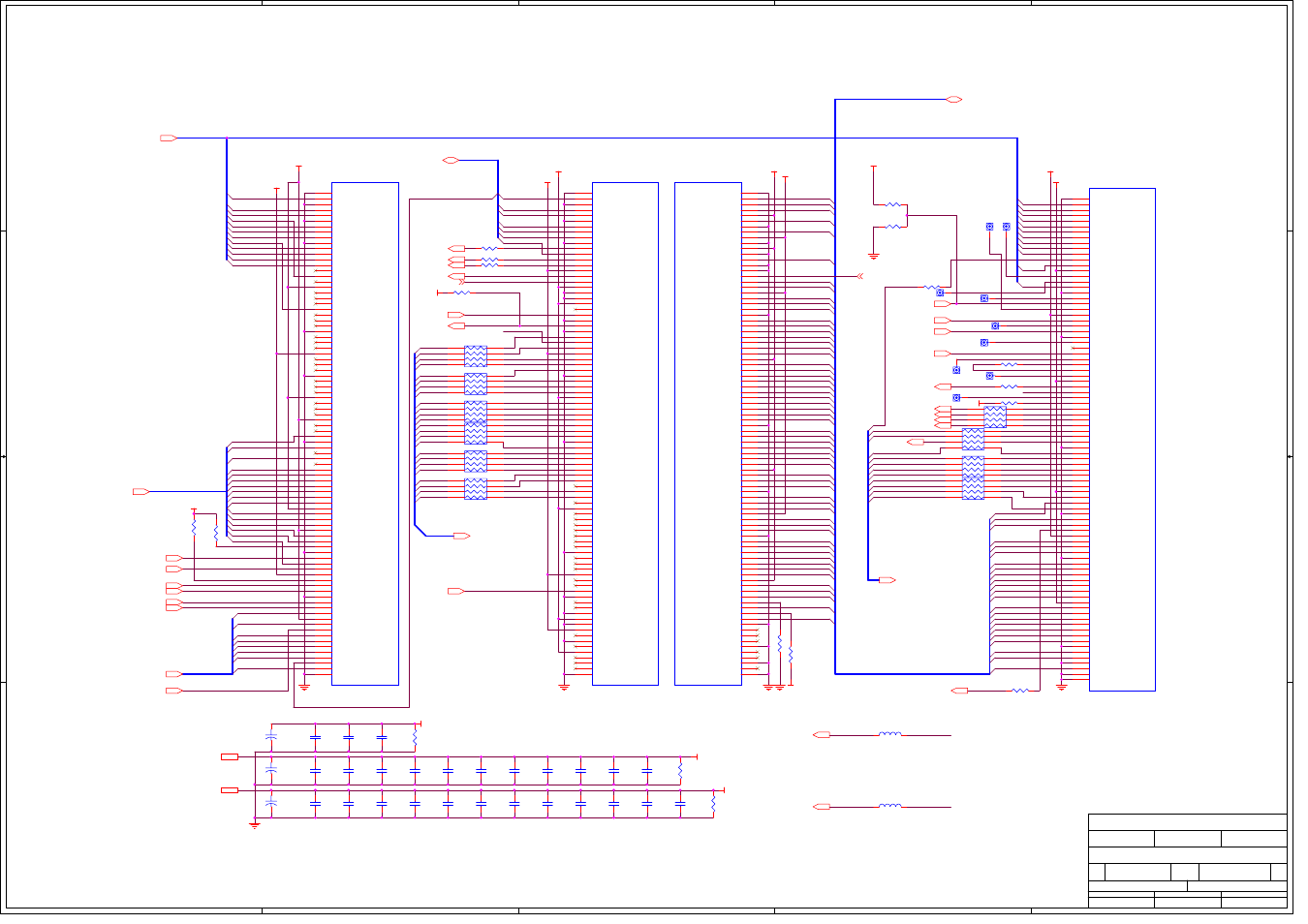

Benq corporation, Modify this area – BenQ DLP PROJECTOR PE8700 User Manual

Page 75

5

5

4

4

3

3

2

2

1

1

D

D

C

C

B

B

A

A

MEM_DQ[0..79]

V _IN[0..15]

D_ INA[0..23]

M

EM_A[0..11]

RM1_D_VALID

RM1_DPLL_CLK

RM1_MEM_RAS_N

RM1_MEM_A5

RM1_MEM_A0

RM1_MEM_A7

RM1_MEM_BS

MEM_DQ47

MEM_DQ29

MEM_DQ27

MEM_DQ26

MEM_DQ25

MEM_DQ46

MEM_DQ45

MEM_DQ44

MEM_DQ43

MEM_DQ42

MEM_DQ41

MEM_DQ40

MEM_DQ39

MEM_DQ38

MEM_DQ37

MEM_DQ36

MEM_DQ35

MEM_DQ33

MEM_DQ32

MEM_DQ30

MEM_DQ28

MEM_DQ31

MEM_DQ34

MEM_DQ22

MEM_DQ24

MEM_DQ23

MEM_DQ18

MEM_DQ20

MEM_DQ19

MEM_DQ21

MEM_DQ17

MEM_DQ13

MEM_DQ14

MEM_DQ15

MEM_DQ10

MEM_DQ12

MEM_DQ9

MEM_DQ11

MEM_DQ6

MEM_DQ8

MEM_DQ7

MEM_DQ2

MEM_DQ4

MEM_DQ5

MEM_DQ3

MEM_DQ1

MEM_DQ0

V_VS YNC

CPU_R D_N

V_ACTIVE

V _HSYNC

VCLK

RM1_CS_N

V_IN0

V_IN3

V_IN4

V_IN2

V_IN6

V_IN8

V_IN7

V_IN5

V_IN10

V_IN11

V_IN9

V_IN13

V_IN14

V_IN12

V_IN15

V_IN1

ADC_SYNC _INV

RM1_MEM_WE_N

RM1_MEM_DQM_U

RM1_MEM_CS_N

RM1_MEM_DQM_L

D_INA21

D_ INA2

D_ INA7

D_INA20

D_ INA3

D_ INA1

D_INA17

D_INA10

D_ INA8

D_INA14

D_INA16

D_INA13

D_INA23

D_INA11

D_INA18

D_INA12

D_INA15

D_INA22

D_INA19

D_ INA9

D_ INA5

D_ INA0

D_ INA6

D_ INA4

RM1_WR_N

OVERFLOW2

MEM_A1

MEM_A3

MEM_A11

RM1_ADC_CLKB

RM1_DPLL_DIV

RM1_TMS

RM1_NTRST

RM1_MCLK_IN

RM1_MCLK_OUTB

RM1_D_FIELD

WIRE_TP31

WIRE_TP30

V_FIELD

V_VALID

RM1_MCLK_OUT

MEM_A9

MEM_A4

MEM_A10

MEM_A8

RM1_MEM_A9

RM1_MEM_A4

RM1_MEM_A10

RM1_MEM_A8

MEM_A6

MEM_A0

MEM_A2

MEM_A7

RM1_MEM_A6

RM1_MEM_A2

MEM_A5

RM1_MEM_A1

RM1_MEM_A3

RM1_MEM_CAS_N

MEM_DQ16

RM1CLKIN

R M1_OP_HSYNC

OP_FIELD

OUT_A3

OUT_A4

RM1_OP_VSYNC

CP U_D7

OUT_A20

OUT_A13

CP U_D1

CP U_D2

CP U_D5

RM1_OCLK_OUT

OUT_A9

OUT_A2

CP U_D6

OUT_A5

CPU_ D[0..7]

OUT_A12

OUT_A6

CP U_D0

OUT_A10

OUT_A21

OUT_A11

CP U_D0

RM1_RST_N

OUT_A16

CP U_D3

RM1_OP_ENABLE

RM1CLKIN

OUT_A15

OUT_A0

CP U_D4

OUT_A22

OUT_A7

OUT_A1

OUT_A8

OUT_A23

MEM_DQ79

MEM_DQ76

MEM_DQ75

MEM_DQ77

MEM_DQ78

MEM_DQ71

MEM_DQ73

MEM_DQ72

MEM_DQ74

MEM_DQ68

MEM_DQ69

MEM_DQ70

MEM_DQ65

MEM_DQ67

MEM_DQ66

MEM_DQ62

MEM_DQ64

MEM_DQ63

MEM_DQ60

MEM_DQ61

MEM_DQ59

MEM_DQ57

MEM_DQ58

MEM_DQ51

MEM_DQ56

MEM_DQ54

MEM_DQ55

MEM_DQ52

MEM_DQ50

MEM_DQ53

MEM_DQ48

MEM_DQ49

CPU_A0

CPU_A7

CPU_A1

CPU_A6

CPU_A3

CPU_A4

CPU_A2

CPU_A5

CLAMP_TESTPIN

DPLL_COAST

OP_A0

OP_A4

OP_A18

OP_A12

OP_A15

OP_A1

OP_A9

OUT_A19

OP_A22

OP_A10

OP_A14

OP_A6

OP_A7

OP_A5

OP_A20

OP_A13

OP_A21

OP_A3

OP_A23

OP_A2

OP_A8

OUT_A18

OUT_A14

OP_A19

OP_A11

OP_A16

OUT_A17

OP_A17

RM1_MCLK_OUT

RM1_OCLK_OUT

MEM_DQ[0..79]

DIN_CLK

D _VSYNC

D_HS YNC

D_INA[0..23]

CPU_D[0..7]

V_IN[0..15]

V_VSYNC

V _HSYNC

V_ACTIVE

VCLK

RM1_CS_N

RM1_WR_N

CPU_RD_N

+1_8V

+3VA

MEM_RAS_N

MEM_WE_N

MEM_DQM_U

MEM_BS

MEM_CAS_N

MEM_CS_N

MEM_DQM_L

MEM_A[0..11]

OP_ENABLE

OP_HSYNC

OP_VSYNC

OP_A[0..23]

RM1_IRQ

RM1_RST_N

OP_FIELD

RM1CLKIN

CPU_A[0..7]

MEM_CLK

OCLK_OUT

DVI_ACTDATA

+3VA

+3VA

+1_8V

+3VA

+1_8V

+3VA

+3VA

+1_8V

+3VA

+3VA

+3VA

+1_8V

+3VA

+3VA

+1_8V

+3VA

RM1CLKIN

RM1CLKIN

Title

Size

Document Number

R e v .

Date:

Sheet

o f

Project Code

Reviewed By

Approved By

Prepared By

Model Name

PCB P/N

P CB Rev.

Benq Corporation

OEM/ODM Model Name

99.J5877.R22-C3-304-001

MAIN BOARD

6

10

COLIN CHANG

BEN CHEN

48.J5801.S02

S02

ANGEL HU

HT720G

99.J5877.001

0

Thursday, January 16, 2003

NA

TOP EDGE

RIGHT EDGE

BOTTOM EDGE

LEFT EDGE

Place the resistors as close to the RM1

pins as possible.

RED -- D_INA[23..16]

GREEN -- D_INA[15..8]

BLUE -- D_INA[7..0]

RM1_GP0 , RM1_GP1

Input Only or Output Only

YUV422

Y -- V_IN[15..8]

UV -- V_IN[7..0]

RED -- OP_A[23..16]

GREEN -- OP_A[15..8]

BLUE -- OP_A[7..0]

24.576MHz

MPLL_CLK_IN , OPLL_CLK_IN ,

PPLL_CLK_IN are 24.576MHz

From Pin AE9,

Former R22

From Pin B12,

Former R25

modify this area

RP10

47_RP

3

4

7

8

5

6

1

2

C46

0.1UF

TP30

E1

1

C45

0.1UF

R15

180

C56

0.1UF

C68

0.1UF

R14

120

R17

33

C66

0.1UF

U5A

VDP01

GND

A1

D_INA12

B1

GND

B2

D_INA14

C1

D_INA13

C2

GND

C3

D_INA17

D1

D_INA15

D2

D_INA16

D3

GND

D4

D_INA21

E1

D_INA18

E2

D_INA20

E3

D_INA19

E4

D_INB1

F1

D_INA22

F2

D_INB0

F3

VDD50

F4

D_INB3

G1

D_INB2

G2

D_INB4

G3

D_INA23

G4

D_INB6

H1

D_INB5

H2

D_INB7

H3

GND

H4

D_INB9

J1

D_INB8

J2

D_INB11

J3

VDD18

J4

D_INB12

K1

D_INB10

K2

D_INB14

K3

GND

K4

D_INB15

L1

D_INB13

L2

D_INB18

L3

VDD50

L4

D_INB17

M1

D_INB16

M2

D_INB21

M3

VDD33

M4

D_INB20

N1

D_INB19

N2

V_IN1

N3

GND

N4

V_IN0

P1

D_INB22

P2

V_IN3

P3

D_INB23

P4

V_IN4

R1

V_IN2

R2

V_IN6

R3

V_IN8

R4

V_IN7

T1

V_IN5

T2

V_IN10

T3

VDD50

T4

V_IN11

U1

V_IN9

U2

V_IN13

U3

VDD33

U4

V_IN14

V1

V_IN12

V2

V_VALID

V3

GND

V4

VCLK

W1

V_IN15

W2

V_HSYNC

W3

VDD18

W4

V_FIELD

Y1

V_ACTIVE

Y2

RD_N

Y3

GND

Y4

CS_N

AA1

V_VSYNC

AA2

AD1

AA3

VDD33

AA4

AD0

AB1

WR_N

AB2

AD5

AB3

AD3

AB4

AD4

AC1

AD2

AC2

AD7

AC3

DB0

AD1

AD6

AD2

GND

AE1

R24

33

C65

0.1UF

L8

Z1000/100MHZ

R28

1K

C71

0.1UF

C48

0.1UF

C58

0.1UF

C69

0.1UF

C44

0.1UF

R16

33

U5C

VDP01

GND

B26

MEM_DQ22

C25

MEM_DQ24

C26

MEM_DQ23

D24

VDD33

D25

MEM_DQ20

D26

GND

E23

MEM_DQ21

E24

VDD18

E25

GND

E26

VDD33

F23

GND

F24

MEM_DQ19

F25

TEST

F26

GND

G23

MPLL_CLK_IN

G24

MEM_DQ16

G25

MEM_DQ17

G26

VDD18

H23

MEM_DQ18

H24

MEM_DQ13

H25

MEM_DQ14

H26

GND

J23

MEM_DQ15

J24

MEM_DQ10

J25

MEM_DQ12

J26

MEM_DQ9

K23

MEM_DQ11

K24

MEM_DQ6

K25

MEM_DQ8

K26

VDD33

L23

MEM_DQ7

L24

MEM_DQ2

L25

MEM_DQ4

L26

MEM_DQ5

M23

MEM_DQ3

M24

MEM_DQ79

M25

MEM_DQ1

M26

MEM_DQ76

N23

MEM_DQ0

N24

MEM_DQ75

N25

MEM_DQ77

N26

GND

P23

MEM_DQ78

P24

MEM_DQ71

P25

MEM_DQ73

P26

MEM_DQ72

R23

MEM_DQ74

R24

MEM_DQ68

R25

MEM_DQ69

R26

VDD33

T23

MEM_DQ70

T24

MEM_DQ65

T25

MEM_DQ67

T26

GND

U23

MEM_DQ66

U24

MEM_DQ62

U25

MEM_DQ64

U26

VDD18

V23

MEM_DQ63

V24

MEM_DQ60

V25

MEM_DQ61

V26

GND

W23

MEM_DQ59

W24

MEM_DQ57

W25

MEM_DQ58

W26

MEM_DQ51

Y23

MEM_DQ56

Y24

MEM_DQ54

Y25

MEM_DQ55

Y26

VDD33

AA23

MEM_DQ52

AA24

MEM_DQ50

AA25

MEM_DQ53

AA26

NTRST

AB23

MEM_DQ48

AB24

TMS

AB25

MEM_DQ49

AB26

GND

AC23

TDI

AC24

TCK

AC25

TDO

AC26

GND

AD24

OP_B1

AD25

OP_B0

AD26

GND

AE25

OP_B2

AE26

GND

AF26

+

C59

10UF/16

RP19 33_RP

1

2

3

4

5

6

7

8

C52

0.1UF

+

C43

10UF/16

R30

1K

U5B

VDP01

GND

AF1

DB1

AF2

GND

AE2

DB3

AF3

DB2

AE3

GND

AD3

DB6

AF4

DB4

AE4

DB5

AD4

GND

AC4

OP_ENABLE

AF5

DB7

AE5

OP_HSYNC

AD5

OP_VSYNC

AC5

VDD18

AF6

OP_FIELD

AE6

OPLL_CLK_IN

AD6

VDD33

AC6

GND

AF7

GND

AE7

VDD33

AD7

OP_FIELD_3D

AC7

RST_N

AF8

GND

AE8

IRQ

AD8

GND

AC8

OP_A23

AF9

OCLK_OUT

AE9

OP_A21

AD9

VDD18

AC9

OP_A20

AF10

OP_A22

AE10

OP_A18

AD10

GND

AC10

OP_A17

AF11

OP_A19

AE11

OP_A14

AD11

VDD33

AC11

OP_A15

AF12

OP_A16

AE12

OP_A10

AD12

OP_A12

AC12

OP_A11

AF13

OP_A13

AE13

OP_A6

AD13

GND

AC13

OP_A7

AF14

OP_A9

AE14

OP_A4

AD14

OP_A8

AC14

OP_A3

AF15

OP_A5

AE15

OP_A1

AD15

OP_B23

AC15

OP_A0

AF16

OP_A2

AE16

OP_B21

AD16

VDD33

AC16

OP_B20

AF17

OP_B22

AE17

OP_B17

AD17

OP_B19

AC17

OP_B16

AF18

OP_B18

AE18

OP_B13

AD18

GND

AC18

OP_B14

AF19

OP_B15

AE19

OP_B10

AD19

VDD18

AC19

OP_B11

AF20

OP_B12

AE20

PPLL_CLK_IN

AD20

GND

AC20

OP_B8

AF21

OP_B9

AE21

GND

AD21

VDD33

AC21

GND

AF22

VDD18

AE22

OP_B6

AD22

GND

AC22

OP_B7

AF23

VDD33

AE23

OP_B4

AD23

OP_B3

AF24

OP_B5

AE24

GND

AF25

C55

0.1UF

R32

1K

R20

NC_R0603

RP18

47_RP

1

2

5

6

7

8

3

4

RP15 33_RP

1

2

3

4

5

6

7

8

C53

0.1UF

RP16

47_RP

1

2

5

6

3

4

7

8

R34

1K

RP14

47_RP

3

4

1

2

5

6

7

8

C50

0.1UF

R29

1K

C49

0.1UF

R33

1K

R18

33

R31

33

C54

0.1UF

TP31

E1

1

U5D

VDP01

GND

A2

D_INA11

A3

D_INA9

B3

D_INA7

A4

D_INA5

B4

D_INA10

C4

D_INA3

A5

D_INA2

B5

D_INA8

C5

D_INA6

D5

D_INA0

A6

DINA_OVERFLOW2

B6

D_INA4

C6

VDD33

D6

DINA_OVERFLOW0

A7

D_FIELD

B7

D_INA1

C7

GND

D7

D_VALID

A8

DIN_CLK

B8

DINA_OVERFLOW1

C8

VDD18

D8

D_VSYNC

A9

DPLL_CLK

B9

D_ACTIVE

C9

GND

D9

CLAMP

A10

ADC_CLK

B10

D_HSYNC

C10

ADC_SYNC_INV

D10

MCLK_IN

A11

MCLK_OUTB

B11

ADC_CLKB

C11

VDD33

D11

MEM_RAS_N

A12

MCLK_OUT

B12

DPLL_COAST

C12

DPLL_DIV

D12

MEM_WE_N

A13

MEM_DQM_U

B13

MEM_CS_N

C13

MEM_DQM_L

D13

MEM_A1

A14

MEM_A3

B14

MEM_CAS_N

C14

GND

D14

MEM_A5

A15

MEM_A6

B15

MEM_A0

C15

MEM_A2

D15

MEM_A7

A16

MEM_A9

B16

MEM_A4

C16

VDD33

D16

MEM_A10

A17

MEM_DQ47

B17

MEM_A8

C17

GND

D17

MEM_DQ46

A18

MEM_DQ45

B18

MEM_BS

C18

VDD18

D18

MEM_DQ43

A19

MEM_DQ42

B19

MEM_DQ44

C19

GND

D19

MEM_DQ40

A20

MEM_DQ39

B20

MEM_DQ41

C20

MEM_DQ36

D20

MEM_DQ38

A21

MEM_DQ35

B21

MEM_DQ37

C21

VDD33

D21

MEM_DQ34

A22

MEM_DQ31

B22

MEM_DQ33

C22

MEM_DQ32

D22

MEM_DQ30

A23

MEM_DQ28

B23

MEM_DQ29

C23

GND

D23

MEM_DQ27

A24

MEM_DQ26

B24

GND

C24

MEM_DQ25

A25

GND

B25

GND

A26

TP32

E1

1

TP50

E1

1

+

C47

10UF/16

C64

0.1UF

TP49

E1

1

TP33

E1

1

C51

0.1UF

R27

1K

RP13 33_RP

1

2

3

4

5

6

7

8

C63

0.1UF

TP34

E1

1

L9

Z1000/100MHZ

R19

33

C61

0.1UF

TP35

E1

1

C57

0.1UF

RP12

47_RP

3

4

1

2

7

8

5

6

C70

0.1UF

C67

0.1UF

TP36

E1

1

C62

0.1UF

RP17 33_RP

1

2

3

4

5

6

7

8

R23

0

C60

0.1UF

R26

NC_R0603

RP11

47_RP

1

2

3

4

5

6

7

8