5v switching characteristics, 3v switching characteristics, Cs5509 – Cirrus Logic CS5509 User Manual

Page 7

CS5509

DS125F3

7

Notes: 16. If CS is activated asynchronously to DRDY, CS will not be recognized if it occurs when DRDY is high

for 2 clock cycles. The propagation delay time may be as great as 2 f

clk

cycles plus 200 ns. To guarantee

proper clocking of SDATA when using asynchronous CS, SCLK(i) should not be taken high sooner than

2 f

clk

+ 200 ns after CS goes low.

17. SDATA transitions on the falling edge of SCLK. Note that a rising SCLK must occur to enable the serial

port shifting mechanism before falling edges can be recognized.

18. If CS is returned high before all data bits are output, the SDATA output will complete the current data

bit and then go to high impedance.

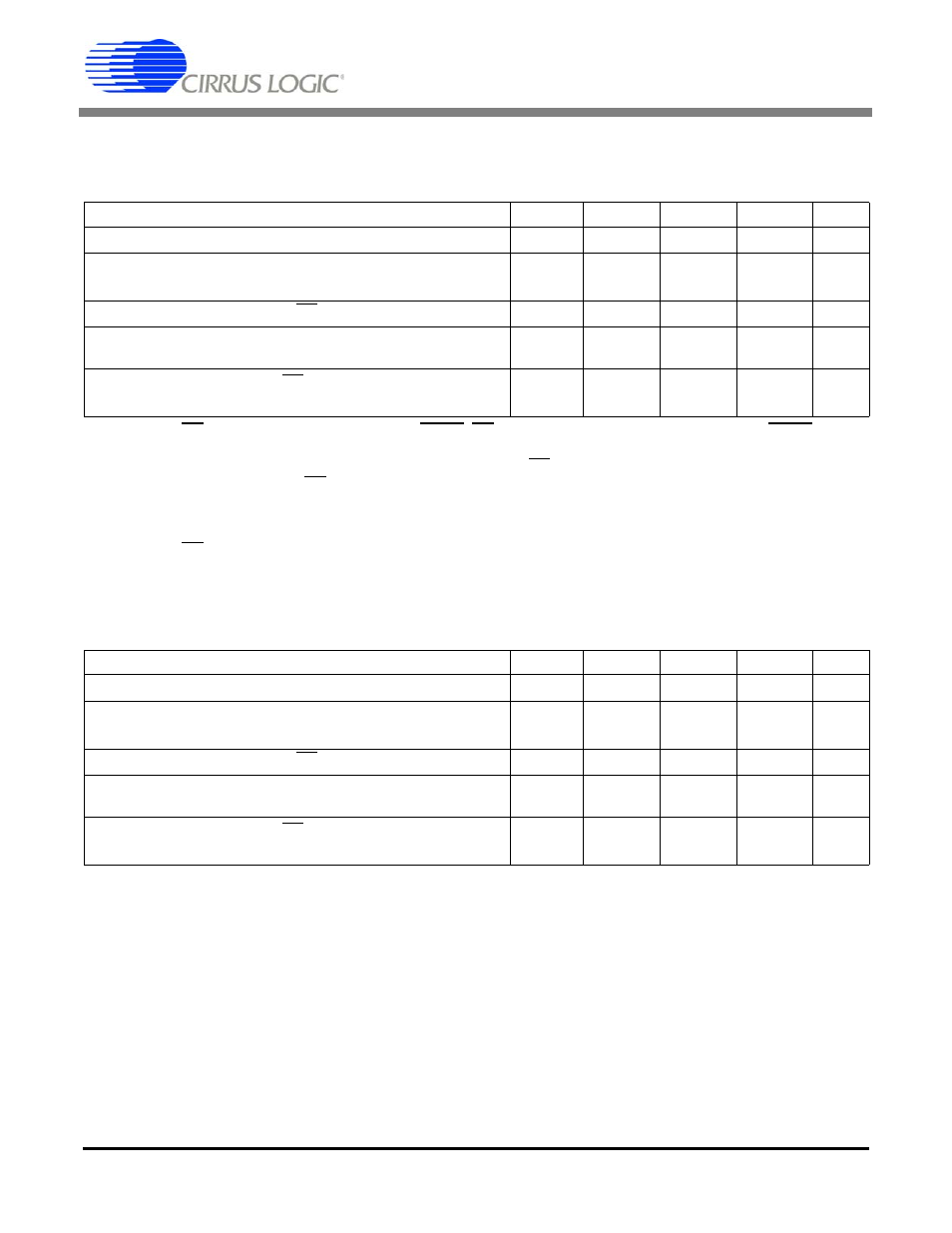

5V SWITCHING CHARACTERISTICS

(T

A

= 25 °C; VA+, VD+ = 5V ±5%; Input Levels: Logic 0 =

0V, Logic 1 = VD+; C

L

= 50 pF) (Note 2)

Parameter

Symbol Min

Typ

Max

Unit

Serial Clock

f

sclk

0

-

2.5

MHz

Serial Clock

Pulse Width High

Pulse Width Low

t

ph

t

pl

200

200

-

-

-

-

ns

ns

Access Time

CS Low to data valid (Note 16)

t

csd

-

60

200

ns

Maximum Delay Time

SCLK falling to new SDATA bit

t

dd

-

150

310

ns

Output Float Delay

CS High to output Hi-Z (Note 18)

SCLK falling to Hi-Z

t

fd1

t

fd2

-

-

60

160

150

300

ns

ns

3.3V SWITCHING CHARACTERISTICS

(T

A

= 25 °C; VA+ = 5V ±5%; VD+ = 3.3V ±5%; Input

Levels: Logic 0 = 0V, Logic 1 = VD+; C

L

= 50 pF) (Note 2)

Parameter

Symbol Min

Typ

Max

Unit

Serial Clock

f

sclk

0

-

1.25

MHz

Serial Clock

Pulse Width High

Pulse Width Low

t

ph

t

pl

200

200

-

-

-

-

ns

ns

Access Time

CS Low to data valid (Note 16)

t

csd

-

100

200

ns

Maximum Delay Time

SCLK falling to new SDATA bit

t

dd

-

400

600

ns

Output Float Delay

CS High to output Hi-Z (Note 18)

SCLK falling to Hi-Z

t

fd1

t

fd2

-

-

70

320

150

500

ns

ns