Typical connection diagram, Figure 2. typical connection diagram – Cirrus Logic CS5368 User Manual

Page 9

DS624F5

9

CS5368

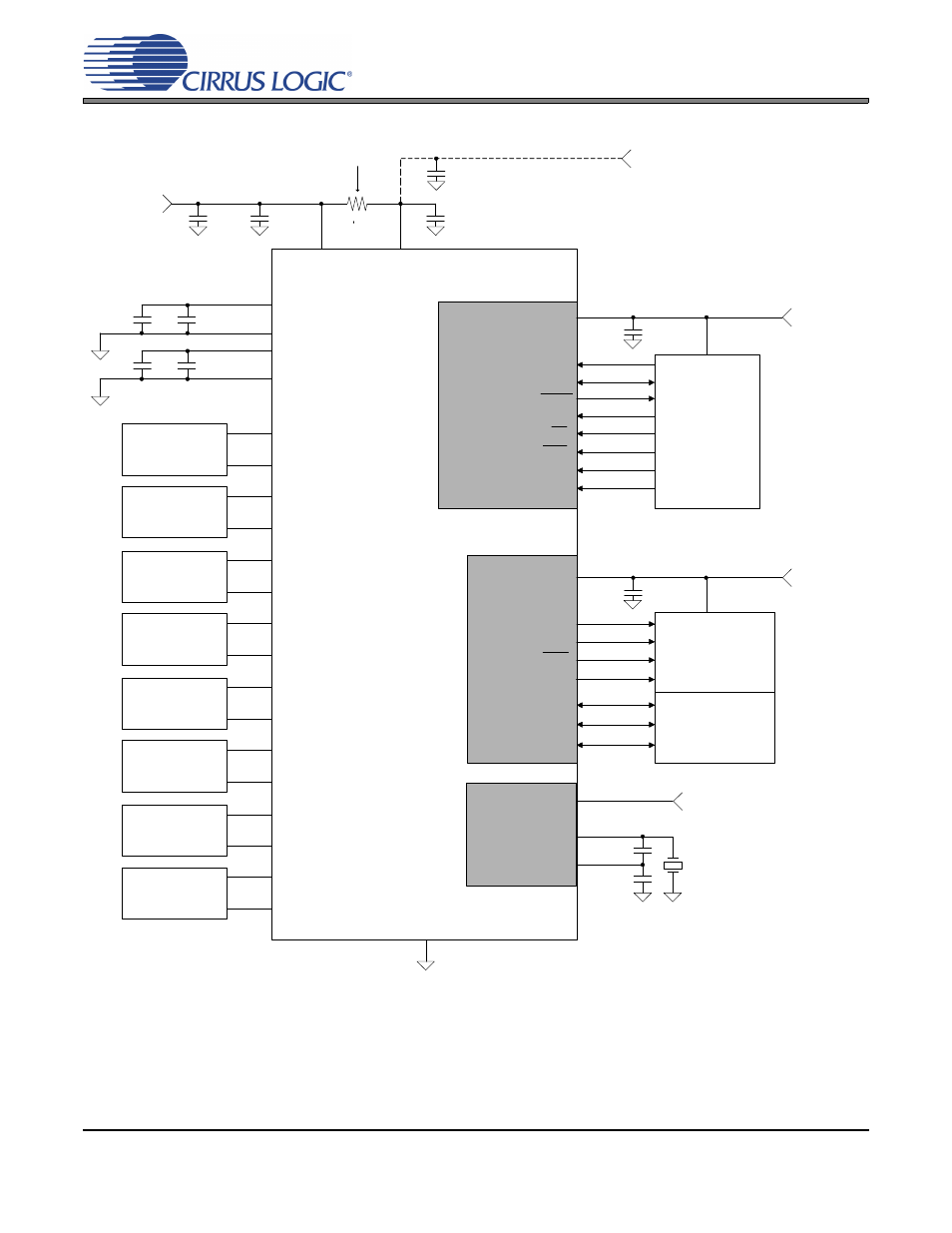

2. TYPICAL CONNECTION DIAGRAM

Figure 2. Typical Connection Diagram

For analog buffer configurations, refer to Cirrus Application Note AN241. Also, a low-cost single-ended-to-differen-

tial solution is provided on the

.

FILT+

D

+

VA

V

+5V

5.1

1 F

+

SDOUT2

DIF0/AD0/CS

Power Down

and Mode

Settings

0.01

F

MODE0/SDA/CDOUT

MODE1/SCL/CCLK

REF_GND

VLC

F

AIN +

1

AIN -

1

Channel 1 Analog

Input Buffer

AIN +

2

AIN -

2

Channel 2 Analog

Input Buffer

AIN +

3

AIN -

3

Channel 3 Analog

Input Buffer

AIN +

4

AIN -

4

Channel 4 Analog

Input Buffer

AIN +

5

AIN -

5

Channel 5 Analog

Input Buffer

AIN +

6

AIN -

6

Channel 6 Analog

Input Buffer

AIN +

7

AIN -

7

Channel 7 Analog

Input Buffer

AIN +

8

AIN -

8

Channel 8 Analog

Input Buffer

0.1

F

VQ

GND

220 F

0.1

F

+

1 F

GND

DIF1/AD1/CDIN

RST

OVFL

0.01

0.01

F

+5V to 3.3V

1 F

+

A/D CONVERTER

CS5368

SDOUT1/ TDM

SDOUT4

SCLK

MCLK

Timing Logic

and Clock

Audio Data

Processor

MDIV

CLKMODE

39

40

36

37

38

41

42

34

27

31

30

26

24

25

23

LRCK/FS

+5V to 1.8V

6

5

7

8

47

48

1

2

13

14

11

12

45

46

43

44

15

16

17

18

3, 8, 10,

19, 29, 32

33

4, 9

35

VLS

F

0.01

28

XTI

XTO

21

22

+5V to 1.8V

+5V

VX

20

SDOUT3/ TDM

Resistor may only be used if

VD is derived from VA. If used,

do not drive any other logic

from VD.