System clocking and serial audio interface – Cirrus Logic CS5344 User Manual

Page 9

DS687F4

9

CS5343/4

Draft

2/1/11

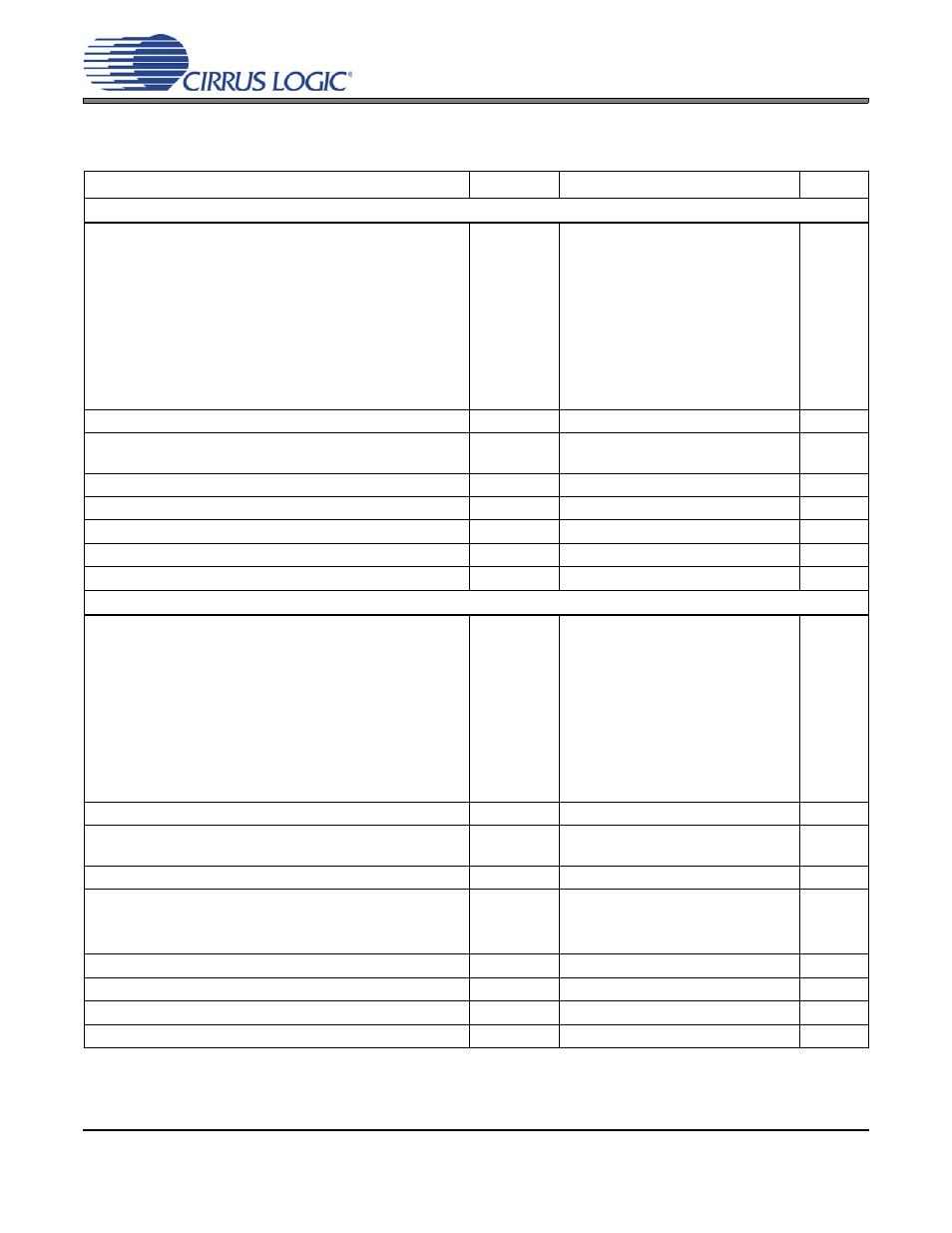

SYSTEM CLOCKING AND SERIAL AUDIO INTERFACE

Logic “0” = GND = 0 V; Logic “1” = VA, C

L

= 20 pF.

Parameter

Symbol

Min

Typ

Max

Unit

Master Mode

MCLK Period

(Double-Speed, 384x Mode)

t

clkw

24

-

30

ns

(Double-Speed, 192x Mode)

48

-

60

ns

(Double-Speed, 256x Mode)

36

-

45

ns

(Double-Speed, 128x Mode)

72

-

90

ns

(Single-Speed, 768x Mode)

24

-

30

ns

(Single-Speed, 384x Mode)

48

-

60

ns

(Single-Speed, 512x Mode)

36

-

45

ns

(Single-Speed, 256x Mode)

72

-

90

ns

MCLK Duty Cycle

40

50

60

%

Output Sample Rate

(Single-Speed)

(Double-Speed)

Fs

43

86

-

-

54

108

kHz

kHz

LRCK Duty Cycle

-

50

-

%

SCLK Duty Cycle

-

50

-

%

SDOUT valid before SCLK rising

t

stp

10

-

-

ns

SDOUT valid after SCLK rising

t

hld

40

-

-

ns

SCLK falling to LRCK edge

t

slrd

-20

-

20

ns

Slave Mode

MCLK Period

(Double-Speed, 384x Mode)

t

clkw

24

-

30

ns

(Double-Speed, 192x Mode)

48

-

60

ns

(Double-Speed, 256x Mode)

36

-

45

ns

(Double-Speed, 128x Mode)

72

-

90

ns

(Single-Speed, 768x Mode)

24

-

325

ns

(Single-Speed, 384x Mode)

48

-

651

ns

(Single-Speed, 512x Mode)

36

-

488

ns

(Single-Speed, 256x Mode)

72

-

976

ns

MCLK Duty Cycle

40

50

60

%

Input Sample Rate

(Single-Speed)

(Double-Speed)

Fs

4

86

-

-

54

108

kHz

kHz

LRCK Duty Cycle

40

50

60

%

SCLK Period

t

sclkw

-

-

ns

SCLK Duty Cycle

45

50

55

%

SDOUT valid before SCLK rising

t

stp

10

-

-

ns

SDOUT valid after SCLK rising

t

hld

40

-

-

ns

SCLK falling to LRCK edge

t

slrd

-20

-

20

ns

1

64

Fs

------------------