Applications, 1 operation as clock master or slave, 1 slave mode operation – Cirrus Logic CS5344 User Manual

Page 12

12

DS687F4

CS5343/4

Draft

2/1/11

4. APPLICATIONS

4.1

Operation as Clock Master or Slave

The CS5343/4 supports operation as either a clock master or slave. As a clock master, the left/right and

serial clocks are synchronously generated on-chip and output on the LRCK and SCLK pins, respectively.

As a clock slave, the LRCK and SCLK pins are always inputs and require external generation of the left/right

and serial clocks. The selection of clock master or slave is made via a 10 k

pull-up resistor from SDOUT

to VA for Master Mode selection or via a 10 k

pull-down resistor from SDOUT to GND for Slave Mode se-

lection, as shown in

.

4.1.1

Slave Mode Operation

A unique feature of the CS5343/4 is the automatic selection of either Single- or Double-Speed Mode when

acting as a clock slave. The auto-mode selection feature supports all standard audio sample rates from

4 to 108 kHz. Please refer to

for supported sample rate ranges in Slave Mode.

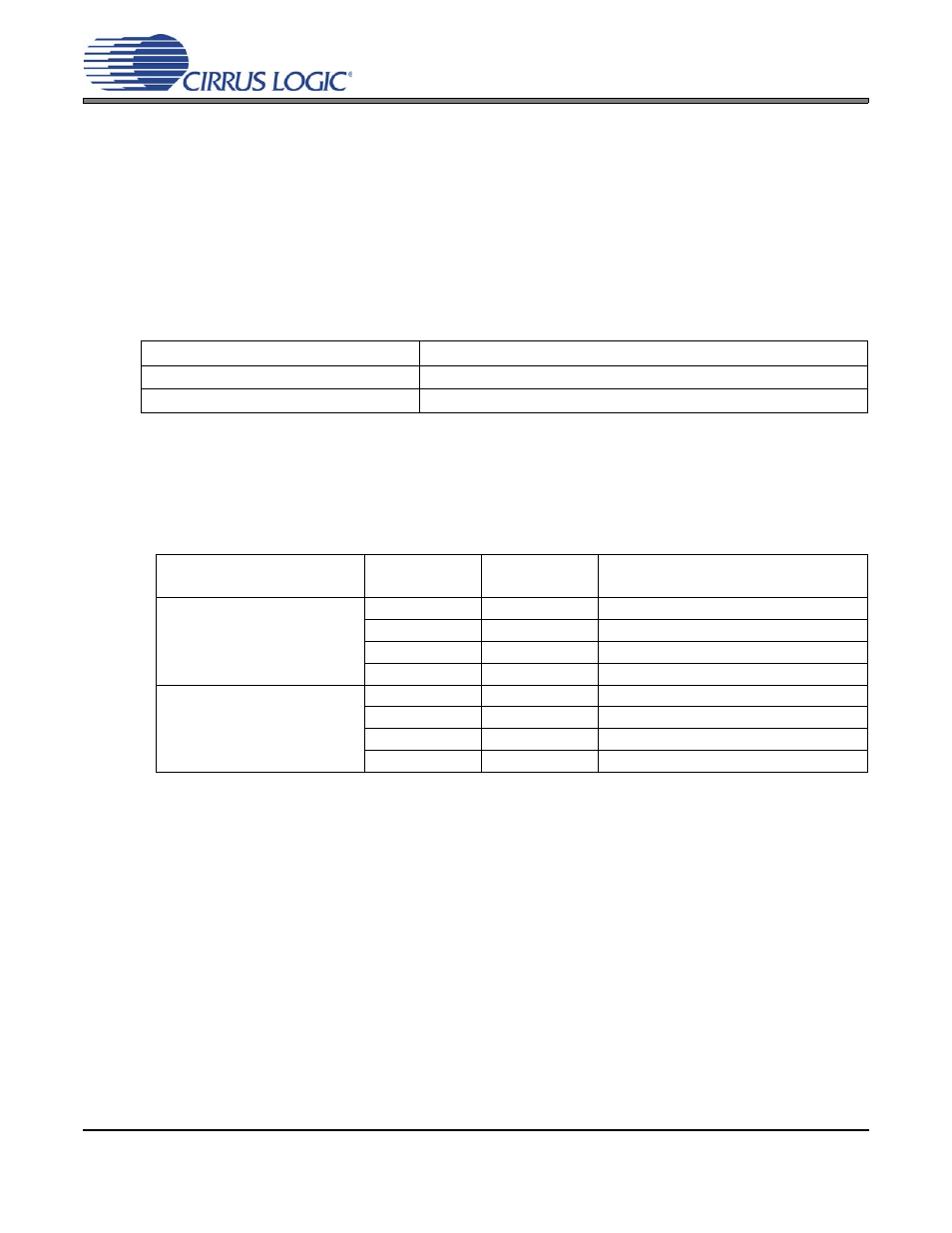

Table 2. Speed Modes and the Associated Sample Rates (Fs) in Slave Mode

Mode

Selection

Master Mode

10 k

pull-up resistor from SDOUT to VA

Slave Mode

10 k

pull-down resistor from SDOUT to GND

Table 1. Master/Slave Mode Selection

Speed Mode

MCLK/LRCK

Ratio

SCLK/LRCK

Ratio

Input Sample Rate Range (kHz)

Single-Speed Mode

256x

64

4 - 54

512x

64

4 - 54

384x

48, 64

4 - 54

768x

48, 64

4 - 54

Double-Speed Mode

128x

64

86 - 108

256x

64

86 - 108

192x

48, 64

86 - 108

384x

48, 64

86 - 108