Cirrus Logic AN333 User Manual

Page 15

AN333

15

4 Operating System (OS) Firmware Module

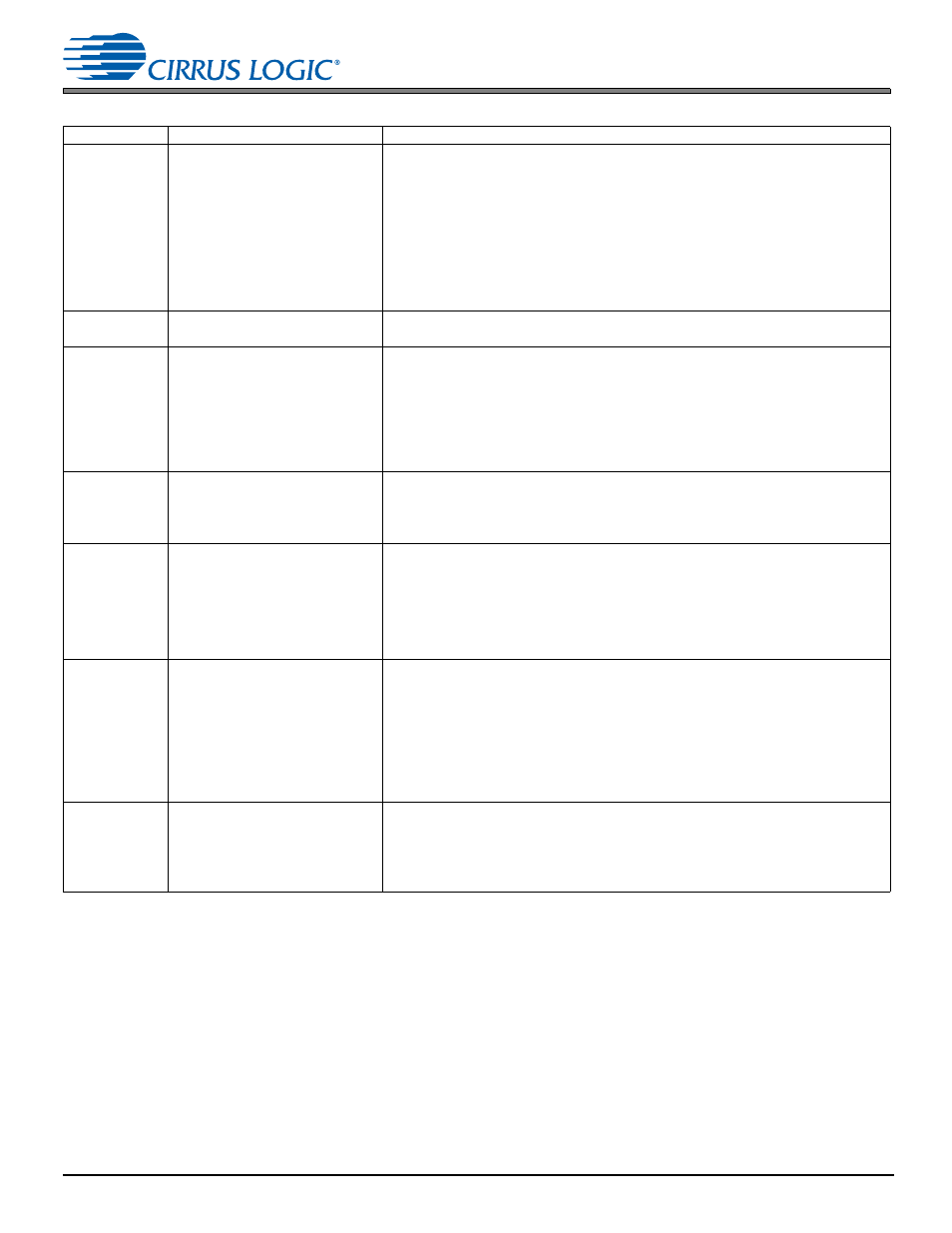

0x0071

OUTPUT_APBSRC_FSI_SEL

Bits 31:1 Reserved

Bit 0 FSI Select:

0x0 - FSI = SPDIFRX_LRCLK

0x1 - FSI = DAI1_LRCLK

1. When output APBSRC is enabled, it must be ensured that DACSRC_FSI_SEL and

OUTPUT_APBSRC_FSI_SEL is the same which could come from either DAI_LRCLK

or SPDIFRX_LRCLK.

2. When output APBSRC is not enabled, variable OUTPUT_APBSRC_FSI_SEL is

irrelevant, however DACSRC_FSI_SEL must be set to 2 (DAO1_LRCLK).

Default = 0x0000 0000

0x0074

PCM_MANUAL_CONFIG†

0/1: Manually Disable/Enable PCM. Autodetect will not have any effect if this is enabled

Default: 0x00000000

0x0075

PCM_AUTOSWITCH_CONFIG†

Bit 0 0/1 Disable/Enable automatic switching to/from PCM Decoder.

Notes:

1) Autodetect must be enabled to use this feature.

2) Valid for Stereo I²S or SPDIF compressed IO_CONFIG values ONLY.”

3) PCM Manager must be enabled to use this feature.

4) If IO_CONFIG is PCM in through SPDIF-RX, Output APBSRC must be enabled.

Default: 0x00000001

0x0076

AUTODETECT_CONFIG†

Bit 2 0/1 Disable/Enable Audio Configuration Change Notification (ACCN).

Bit 1 0/1 Disable/Enable bypassing of autodetection at application restart.

Bit 0 0/1 Disable/Enable autodetection

Default = 0x00000001

0x0077

PCM_AUTODETECT_SILENCE_

THRESHOLD†

Bits 31:0 Number of samples (Left+Right) of silence upon which the DSP will declare

Silence while having detected and currently playing PCM (Autodetect is enabled).

Valid for all decoders when configured for PCM pass-through and auto switch. It is

recommended that system designers set this value large enough to avoid inter-track

silence from PCM compact discs.

Default = 0x00017700

(The default allows for 1 sec of inter-track silence at 48 Khz).

0x0078

SPDIF_RX_STATUS

Read Only

S/PDIF Rx Lock: 0x00000040

S/PDIF Rx Unlock: 0x00000041

Valid only if Bit 21 of Index 0x0001 is set with the following input configurations:

• 0001 8-ch I

2

S PCM

• 0004 8-ch I

2

S PCM with SRC

• 1000 ADC

Refer to

for additional information.

0x007E

RUNTIME_AUTODETECT_IEC_

SYNC_CHECK_CONFIG

MCV sets the number of IEC sync frames (1 or 2) that Autodetect is looking for.

Bit 0

0x0: Perform check for 2 IEC syncs

0x1: Perform check for 1 IEC sync

Default: 0x00000001

1.General notes on indices 0x000A, 0x000B, 0x000C: Timer_Ticks (time between successive timer isrs) = TIMER0_RELOAD_COUNT/DSP_CLOCK.

In other words, for achieving desired frequency of timer ticks, register 0x000B needs to be set after taking cognizance of DSP_CLOCK. Also note the

dependence of values in index 0x000A and 0x000C on the value in index 0x000B.

Table 4-1. OS Firmware Manager (Cont.)

Index

Variable

Description