Cirrus Logic AN333 User Manual

Page 14

14

AN333

4 Operating System (OS) Firmware Module

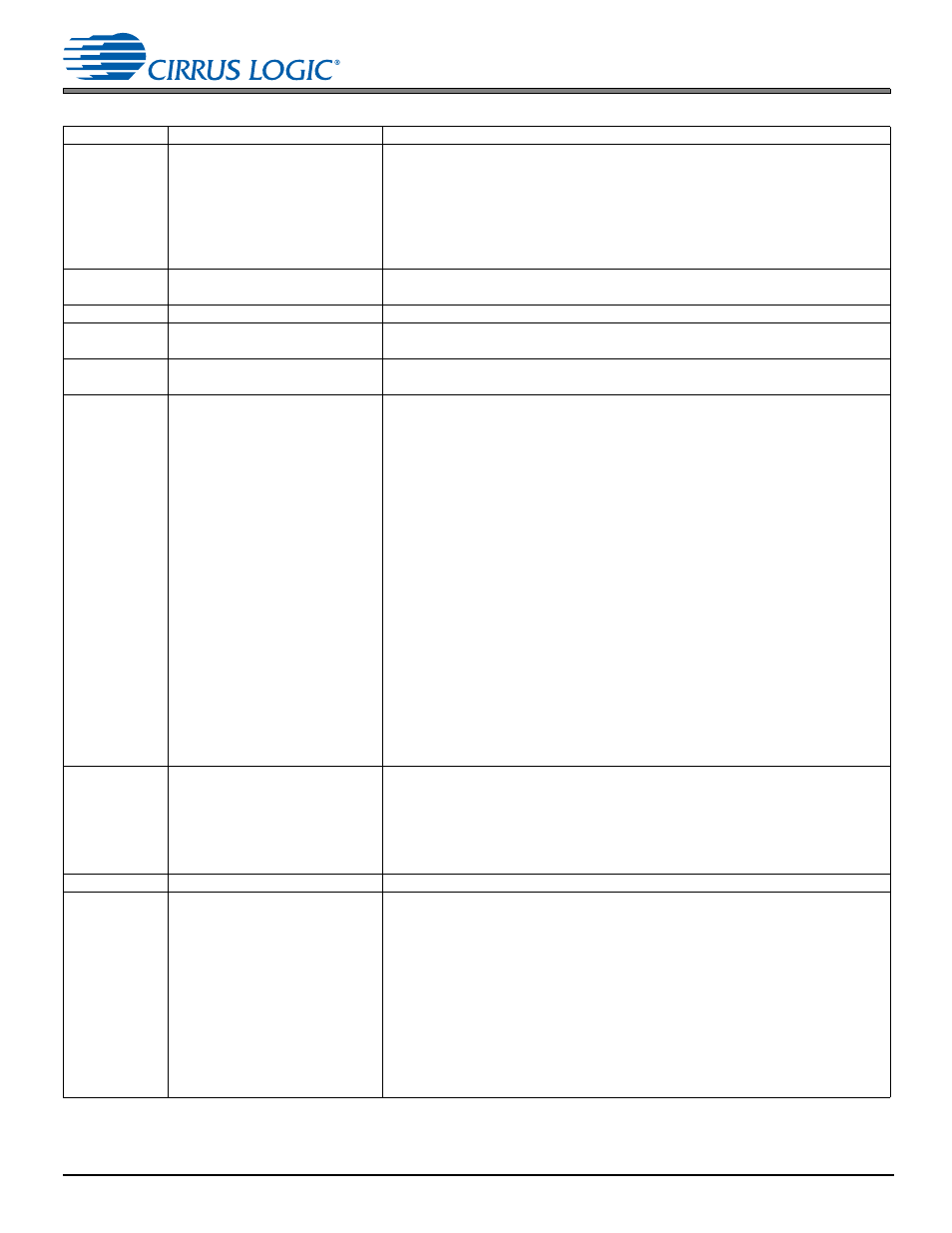

0x0059

SCP_CONTROL

Post pre-kick-start mode of SCP communication

Bits 2 1 0

0 0 0 => I2C Master (Supported for firmware versions V01, V03 only)

0 0 1 => SPI Master (Supported for firmware versions V01, V03 only)

1 0 0 => I2C Slave

1 0 1 => SPI Slave

Default: 0x00000000

0x005D

PLL1_CUSTOM_CONFIG2

Read only

ADC, DAC clock.

0x005E

CLKMGR2_CUSTOM_CONFIG0

Reserved

0x005F

CLKMGR2_CUSTOM_CONFIG1

Read only

S/PDIF Rx clock.

0x0060

CLKMGR2_CUSTOM_CONFIG2

Read only

SRC clock.

0x006D

ADC_USER_MODES

Setting of ADC_USER_MODE. Bits [18:9] can be changed during runtime.

Bits 0:3 ADC_ENABLE for ADCs

1 Enable

0 Disable

Bit 4

1 Enables single-ended operation for all ADCs

0 Differential operation for all ADCs

Bit 5:8 Reserved

Bits 9:13 MUX_SELECT_CH2–ADC

0x01 AIN2A

0x02 AIN3A

0x04 AIN4A

0x08 AIN5A

0x10 AIN6A

Bits 14:18 MUX_SELECT_CH3–ADC

0x01- AIN2B

0x02- AIN3B

0x04- AIN4B

0x08- AIN5B

0x10- AIN6B

Bit 19:31 Reserved

Default: 0x0000 423F

0x006E

DAC_USER_MODES

Bits 3:0 are the DAC_ENABLES (1 = enabled)

Bit 0 = DAC outputs AOUT_1 and AOUT_2

Bit 1 = DAC outputs AOUT_3 and AOUT_4

Bit 2 = DAC outputs AOUT_5 and AOUT_6

Bit 3 = DAC outputs AOUT_7 and AOUT_8

Other bits are reserved and set to 0, except bits 23 and 24 are reserved and set to 1.

0x006F

Reserved

Reserved

0x0070

DACSRC_FSI_SEL

Bits 31:2 Reserved

Bits 1:0 FSI Select:

0x0 - FSI = SPDIFRX_LRCLK

0x1 - FSI = DAI1_LRCLK

0x2 - FSI = DAO1_LRCLK (default)

0x3 - Reserved

When output APBSRC is enabled, it must be ensured that DACSRC_FSI_SEL and

OUTPUT_APBSRC_FSI_SEL is the same which could come from either DAI_LRCLK

or SPDIFRX_LRCLK.

When output APBSRC is not enabled, variable OUTPUT_APBSRC_FSI_SEL is

irrelevant, however DACSRC_FSI_SEL must be set to 2 (DAO1_LRCLK).

Default = 0x0000 0002

Table 4-1. OS Firmware Manager (Cont.)

Index

Variable

Description