Cirrus Logic AN333 User Manual

Page 12

12

AN333

4 Operating System (OS) Firmware Module

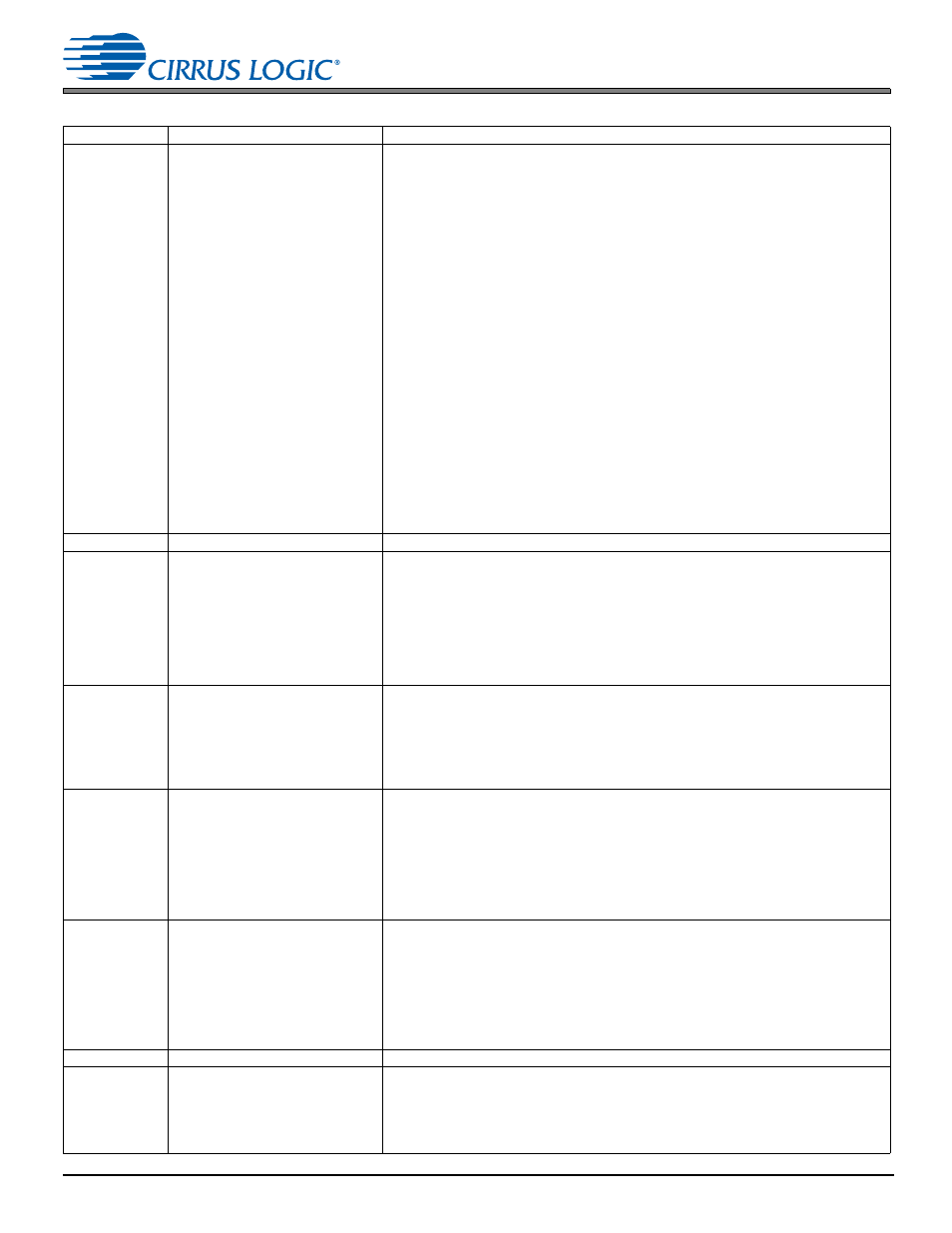

0x0003

SAMPLE_RATE

†

The host must set the sample rate variable to inform firmware modules of the sample

rate. Some firmware modules use this information to calculate correct coefficients or

use the correct table data. The actual sample rate is determined by the DAO_LRCLK,

which can be configured to be master or slave. If the DAO_LRCLK is master, the

sample_rate can be set using the DAO clock dividers. See the CS470xx Hardware

User’s Manual for more information.

Bits 3:0 Sample Rate

0x0 = 48 kHz

0x1 = 44.1 kHz

0x2 = 32 kHz

0x3 = Reserved

0x4 = 96 kHz

0x5 = 88.2 kHz

0x6 = 64 kHz

0x7 = Reserved

0x8 = 24 kHz

0x9 = 22.05 kHz

0xA = 16 kHz

0xB = Reserved

0xC = 192 kHz

0xD = 176.4 kHz

0xE = 128 kHz

0xF = Reserved

Default = 0x00000000 (48 kHz)

0x0004–0x0008

Reserved

Reserved

0x0009

SOFTBOOT

†

Bit 4: 1 = Engage low-power mode.

Bit 0: 0/1 disable/initiate soft boot sequence.

After a soft boot is initiated, the OS sends a 0x00000005 (SOFT_BOOT_ACK) to the

host. The host can then use the standard boot protocol to download one or more

overlays. After a soft boot is initiated, the OS will respond to boot protocol messages

only.

The bit is reset to 0 after the soft boot is complete.

Default = 0x00000000

0x000A

WATCHDOG_CONFIG

1

Specifies the software watch-dog expiry count in terms of timer0 ticks (timer isr counts).

This count is decremented in Timer0 ISR and upon reaching zero system is restarted.

Bits 31:0 0 = Disable Software watchdog.

Default: 0x1000 (corresponds to approximately 4 seconds assuming DSP_CLOCK is

150 MHz and TIMER_RELOAD is 0x249F0).

0x000B

TIMER0_RELOAD_COUNT

1

Specifies the value of TIMER0_RELOAD register from which count down to zero

begins.

TIMER0_COUNT starts with this value and is decremented every processor cycle and

is reloaded back to this value upon reaching zero. Setting this register also sets the

frequency of TIMER0 ISR because timer isr fires whenever TIMER0_COUNT reaches

zero.

Bits 31:0

Default: 0x249F0 (corresponds to 1 millisecond assuming DSP_CLOCK is 150 MHz).

0x000C

TIMER_MODULE_COUNT

1

Specifies the value for frequency of executing timer entry point of modules. The value

is specified in terms of timer0 ticks (timer isr counts).

Bits 31:0

Default: 500 (corresponds to half a second assuming DSP_CLOCK is 150 MHz and

TIMER_RELOAD is 0x249F0).

Note: Since timer entry point of modules is called from BRICK_ISR thread minimum

frequency of occurrence for timer modules is limited to 16/Fs sec (0.33 msec for 48

kHz).

0x000D–0x003A

Reserved

Reserved

0x003B

GPIO_D†

GPIO data register.

Bits 31:0

Bit[i] corresponds to pin GPIO[i] (i=0,...,31).

Both the GPIO_OE and GPIO_MUX must be set to 1 for a particular bit before that bit

can be written. Bit 13 and 12 of KICKSTART variable must be set to 1(enabled).

Table 4-1. OS Firmware Manager (Cont.)

Index

Variable

Description