Cirrus Logic AN333 User Manual

Page 11

AN333

11

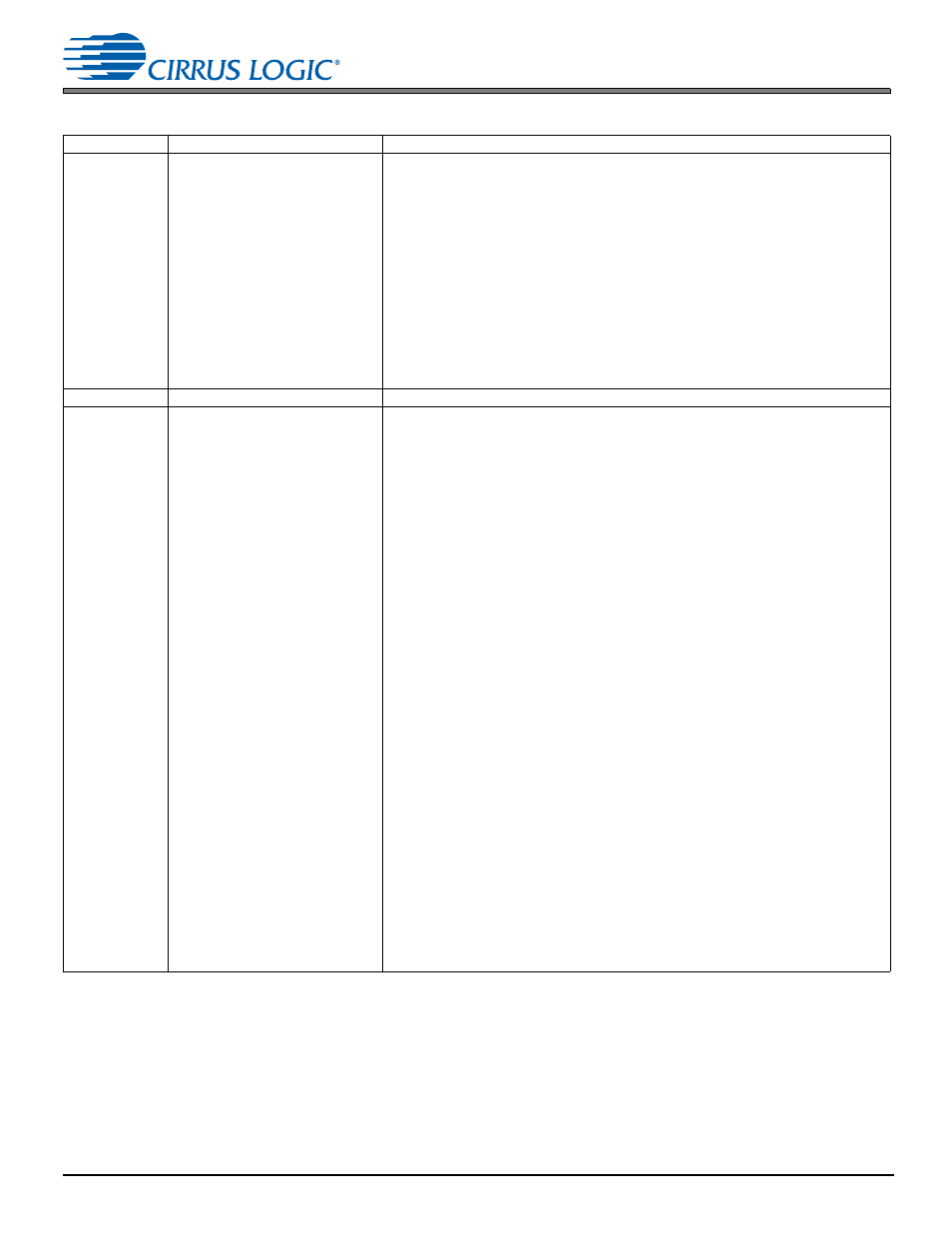

4 Operating System (OS) Firmware Module

Table 4-1. OS Firmware Manager

Index

Variable

Description

0x0000

KICKSTART

Bit 16: 0/1 Disable/enable malloc failure reporting.

Bit 13: 0/1 Disable/enable continual GPIO updating.

Only applicable if Bit 12 is set. If Bit 12 is disabled, audio pins are be available.

Bit 12: 0/1 Disable/enable GPIO updates.

Bit 9: 0/1 Disable/enable hardware watchdog timer reload.

Bit 8: 0/1 Disable/enable hardware watchdog timer.

When Bit 8 is set, the hardware watchdog timer is enabled. When the watchdog timer

is enabled, the timer with the initial set value starts decrementing, and when it reaches

zero, it stops decrementing and resets the hardware. Every 16 audio samples, there is

an option to reload the watchdog timer, controlled by bit 9. If bit 9 is set, a watchdog

timer reload does not take place. Otherwise, the counter is reloaded with the set value

every 16 audio samples.

Bit 0: Kick-start: Set to 1 to trigger kick-start

Default = 0x00000000

0x0001

IO_CONFIG

See

for the details of this index.

0x0002

OUTPUT_MODE_CONTROL

†

Bits 7:4 Dual Mono Mode (valid only if input mode is 0x0000)

0x0 = Stereo Mode => Center_out = None

Left_out = Left_in

Right_out = Right_in

0x1 = Left Mono => Center_out = Left_in

Left_out = None

Right_out = None

0x2 = Right Mono => Center_out = Right_in

Left_out = None

Right_out = None

0x3 = Mixed Mono => Center_out = (Lin+Rin)/2

Left_out = None

Right_out = None

For non-zero values (1,2 or 3) in bits 7:4 of the OUTPUT_MODE_CONTROL variable,

values in bits 3:0 are ignored.

Dual mono mode selection is available only if input mode is 0, that is for dual mono

streams.

Bits 3:0 Output Mode (number of speakers present in the system)

0x0 = 2/0 Lt, Rt Dolby Surround compatible

0x1 = 1/0 C

0x2 = 2/0 L/R

If the output mode is set to 0x02 and Dolby decoding is also set, then the output is Lt/

Rt or Lo/Ro depending on the setting of the AC3 Manager STEREO_MODE_

CONTROL. See AN333DA for more information.

0x3 = 3/0 L/C/R

0x4 = 2/1 L/R/S

0x5 = 3/1 L/C/R/S

0x6 = 2/2 L/R/Ls/Rs

0x7 = 3/2 L/C/R/Ls/Rs

0x8 = 3/3 L/C/R/Ls/Rs/Cs

0x9 = 3/4 L/C/R/Ls/Rs/Sbl/Sbr

0xA = 2/3 L/R/Ls/Rs/Cs

0xB = 2/4 L/R/Ls/Rs/Sbl/Sbr

Default = 0x00000007