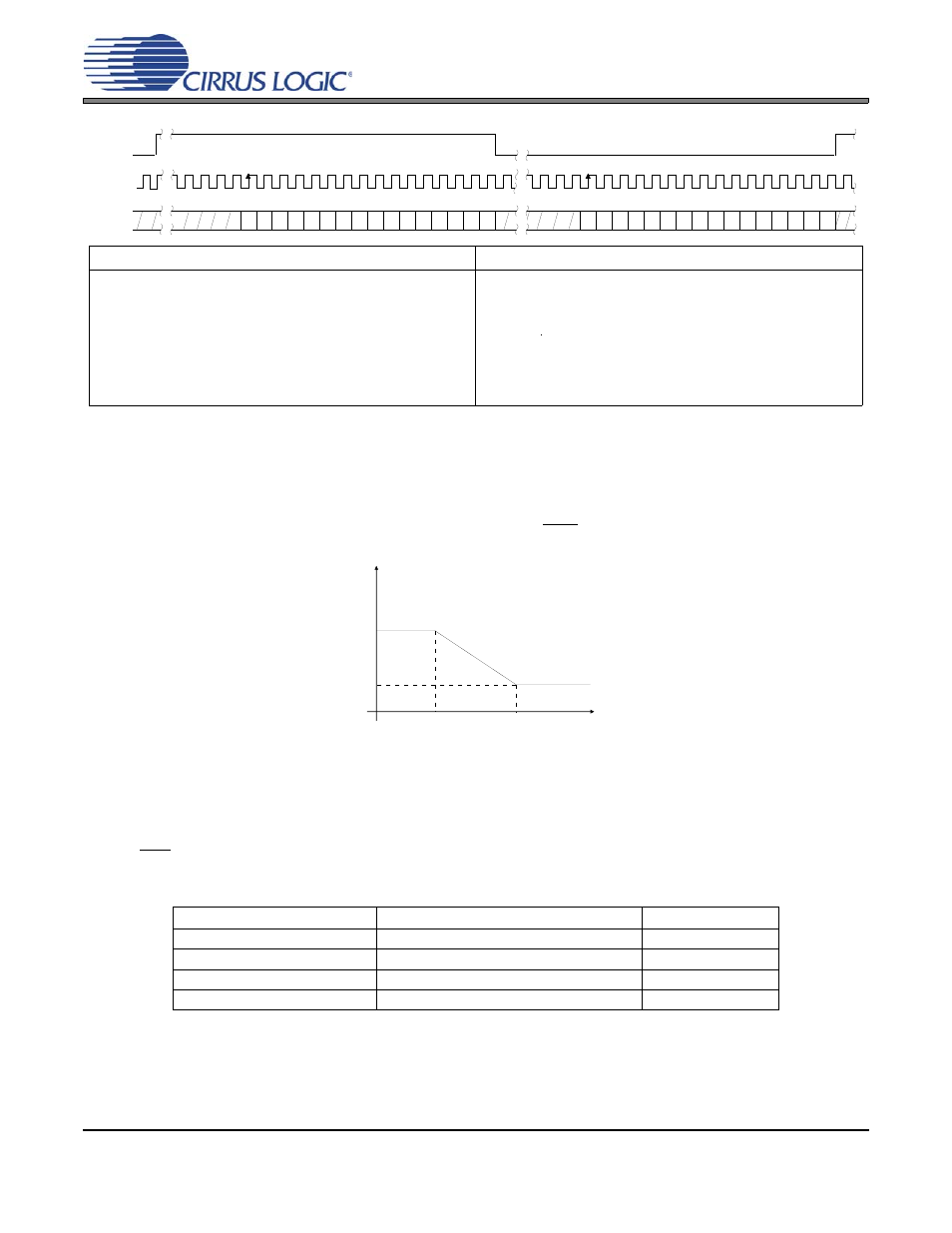

Figure 10. cs4361 data format (right-justified 16), 3 de-emphasis, Figure 11. de-emphasis curve (fs = 44.1khz) – Cirrus Logic CS4361 User Manual

Page 14: 4 mode select, Table 2. mode pin settings, 3 de-emphasis 4.4 mode select

14

CS4361

Confidential Draft

9/30/11

4.3

De-Emphasis

The CS4361 includes on-chip digital de-emphasis.

shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve will scale proportionally with changes in sam-

ple rate, Fs. The de-emphasis filter is active (inactive) if the DEM/SCLK pin is low (high) for five consecutive

falling edges of LRCK. This function is available only in the internal Serial Clock Mode when LRCK < 50 kHz.

4.4

Mode Select

Mode selection is determined by the Mode Select pin. The value of this pin is locked 1024 LRCK cycles after

RST is released. This pin requires a specific connection to supply, ground, MCLK, or LRCK as outlined in

Table 2. Mode Pin Settings

Mode pin is:

Mode

Figure

Tied to VL

I²S

Tied to GND

Left-Justified

Tied to LRCK

Right-Justified - 24 bit

Tied to MCLK

Right-Justified - 16bit

LRCK

SCLK

Left Channel

Right Channel

SDATA

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

6

5

4

3

2

1

0

9

8

7

15 14 13 12 11 10

32 clocks

Internal SCLK Mode

External SCLK Mode

Right-Justified, 16-Bit Data

INT SCLK = 32 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Right-Justified, 16-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 32 Cycles per LRCK Period

Figure 10. CS4361 Data Format (Right-Justified 16)

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1

F2

3.183 kHz

10.61 kHz

Figure 11. De-Emphasis Curve (Fs = 44.1kHz)