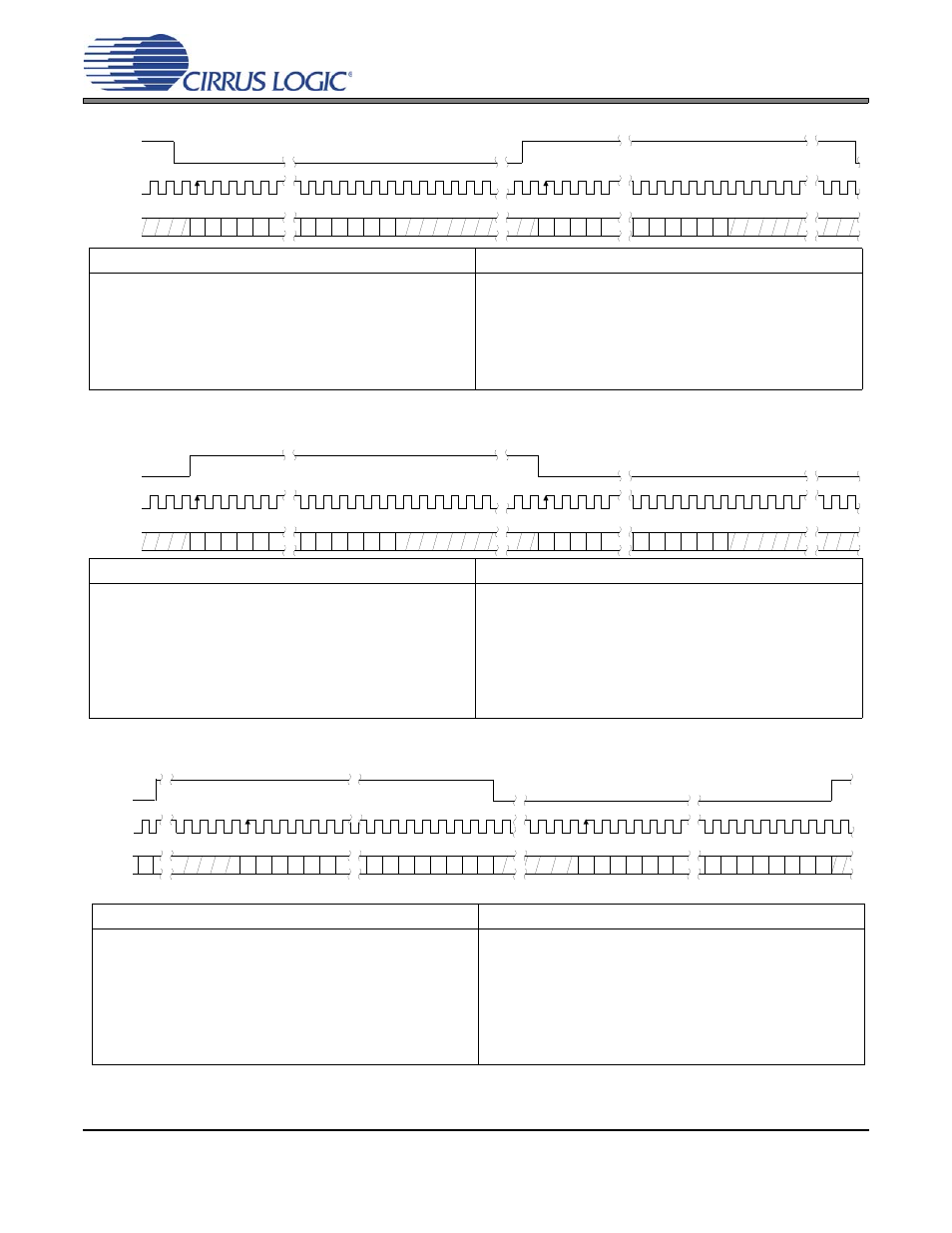

Figure 7. cs4361 data format (i·s), Figure 8. cs4361 data format (left-justified), Figure 9. cs4361 data format (right-justified 24) – Cirrus Logic CS4361 User Manual

Page 13: Figures 7, Fer to

13

CS4361

Confidential Draft

9/30/11

LRCK

SCLK

Left Channel

Right Channel

SDATA

+3 +2 +1 LSB

+5 +4

MSB -1 -2 -3 -4 -5

+3 +2 +1 LSB

+5 +4

MSB -1 -2 -3 -4

Internal SCLK Mode

External SCLK Mode

I²S, 16-Bit data and INT SCLK = 32 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

I²S, Up to 24-Bit data and INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

I²S, Up to 24-Bit data and INT SCLK = 72 Fs if

MCLK/LRCK = 1152

I²S, up to 24-Bit Data

Data Valid on Rising Edge of SCLK

Figure 7. CS4361 Data Format (I²S)

LRCK

SCLK

Left Channel

Right Channel

SDATA

+3 +2 +1 LSB

+5 +4

MSB -1 -2 -3 -4 -5

+3 +2 +1 LSB

+5 +4

MSB -1 -2 -3 -4

Internal SCLK Mode

External SCLK Mode

Left-Justified, up to 24-Bit Data

INT SCLK = 64 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Left-Justified, up to 24-Bit Data

Data Valid on Rising Edge of SCLK

Figure 8. CS4361 Data Format (Left-Justified)

LRCK

SCLK

Left Channel

SDATA

6

5

4

3

2

1

0

7

23 22 21 20 19 18

6

5

4

3

2

1

0

7

23 22 21 20 19 18

32 clocks

0

Right Channel

Internal SCLK Mode

External SCLK Mode

Right-Justified, 24-Bit Data

INT SCLK = 64 Fs if

MCLK/LRCK = 1024, 512, 256, 128, or 64

INT SCLK = 48 Fs if

MCLK/LRCK = 768, 384, 192, or 96

INT SCLK = 72 Fs if

MCLK/LRCK = 1152

Right-Justified, 24-Bit Data

Data Valid on Rising Edge of SCLK

SCLK Must Have at Least 48 Cycles per LRCK Period

Figure 9. CS4361 Data Format (Right-Justified 24)