6 de-emphasis control, Figure 7. de-emphasis curve, fs = 44.1 khz, 7 internal power-on reset – Cirrus Logic CS4353 User Manual

Page 16: Figure 8. internal power-on reset circuit, Cs4353

16

DS803F3

CS4353

4.6

De-emphasis Control

The device includes on-chip digital de-emphasis.

shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve scales with changes in the sample rate, Fs.

The de-emphasis error will increase for sample rates other than 44.1 kHz.

When the DEM pin is connected to VL, the 44.1 kHz de-emphasis filter is activated. When the DEM pin is

connected to GND, the de-emphasis filter is turned off.

Note:

De-emphasis is only available in Single-Speed Mode.

4.7

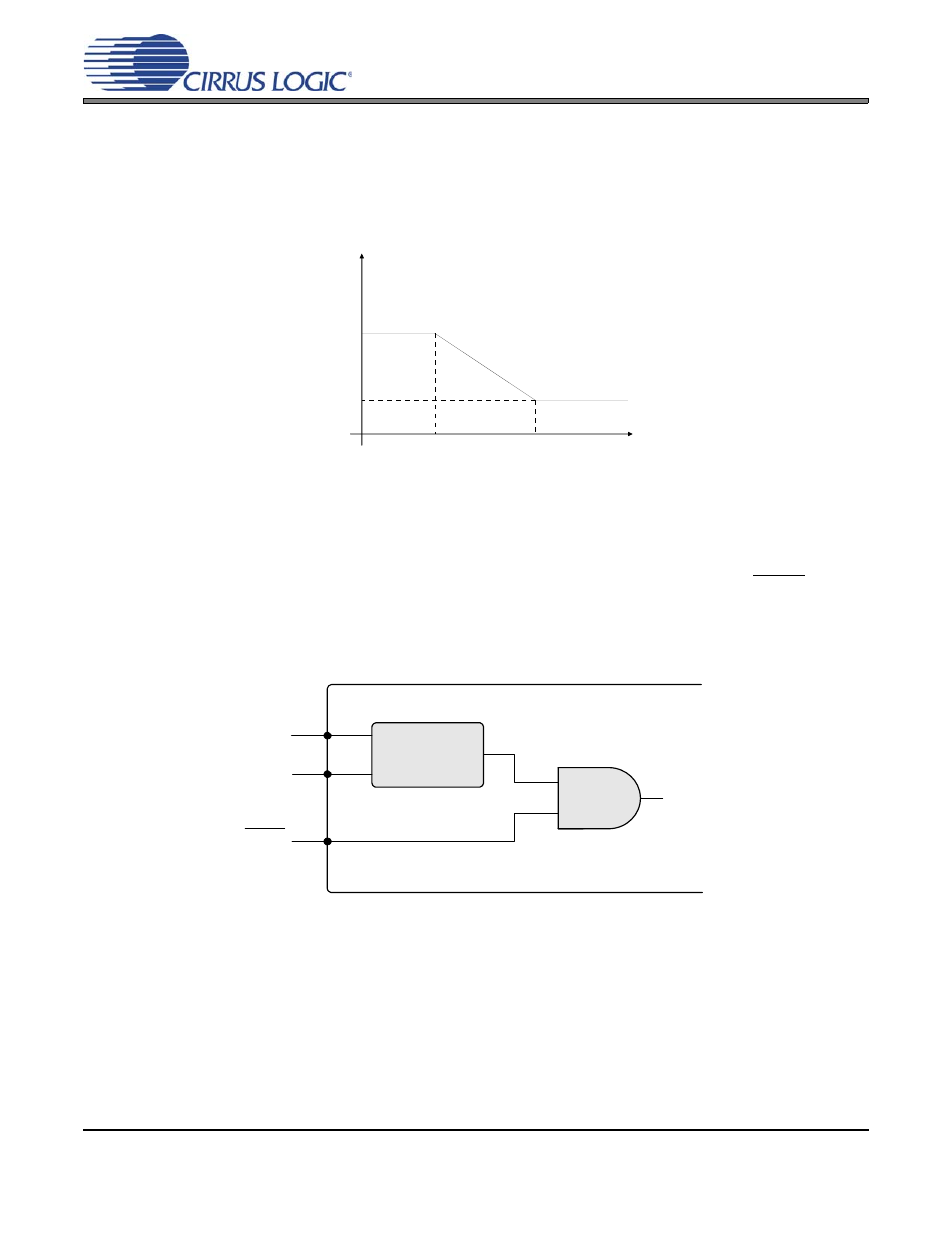

Internal Power-on Reset

The CS4353 features an internal power-on reset (POR) circuit. The POR circuit allows the RESET pin to be

connected to VL during power-up and power-down sequences if the external reset function is not needed.

This circuit monitors the VCP supply and automatically asserts or releases an internal reset of the DAC’s

digital circuitry when the supply reaches defined thresholds (see

“Internal Power-on Reset Threshold Volt-

). No external clocks are required for the POR circuit to function.

Figure 8. Internal Power-on Reset Circuit

When power is first applied, the POR circuit monitors the VCP supply voltage to determine when it reaches

a defined threshold, V

on1

. At this time, the POR circuit asserts the internal reset low, resetting all of the

digital circuitry. Once the VCP supply reaches the secondary threshold, V

on2

, the POR circuit releases the

internal reset.

Note:

For correct operation of the internal POR circuit, the voltage on VL must rise before or simulta-

neously with VCP.

When power is removed and the VCP voltage reaches a defined threshold, V

off

, the POR circuit asserts the

internal reset low, resetting all of the digital circuitry.

Gain

dB

-10dB

0dB

Frequency

T2 = 15 µs

T1=50 µs

F1

F2

3.183 kHz

10.61 kHz

Figure 7. De-emphasis Curve, Fs = 44.1 kHz

RESET

(external)

Power-On Reset

Circuit

VCP

DGND

reset

(internal)