Cs4299 – Cirrus Logic CS4299 User Manual

Page 28

CS4299

28

4.14

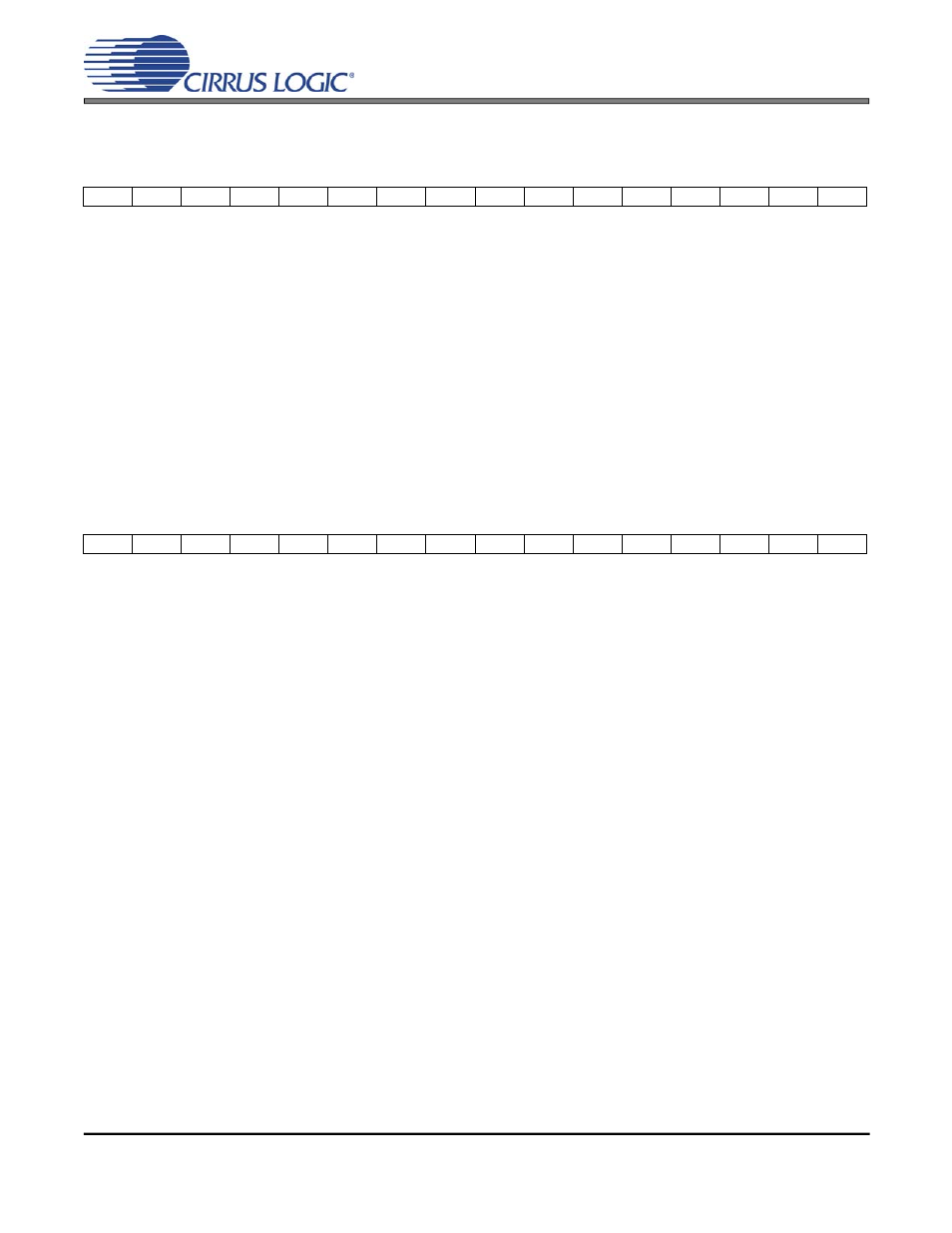

Extended Audio ID Register (Index 28h)

ID[1:0]

Codec Configuration ID. When ID[1:0] = 00, the CS4297A is the primary audio codec. When

ID[1:0] = 01, 10, or 11, the CS4297A is a secondary audio codec. The state of the ID[1:0] bits

is determined at power-up from the ID[1:0]# pins.

AMAP

Audio Slot Mapping. The AMAP bit indicates whether the optional AC ’97 2.1 compliant AC-link

slot to audio DAC mapping is supported. This bit is a shadow of the AMAP bit in the AC Mode

Control Register (Index 5Eh). The PCM playback and capture slots are mapped according to

Table 8 on page 30.

VRA

Variable Rate PCM Audio. The VRA bit indicates whether variable rate PCM audio is supported.

This bit always returns ‘1’, indicating that variable rate PCM audio is available.

Default

x201h. Where x is determined by the state of ID[1:0]# input pins. The Extended Audio ID Reg-

ister (Index 28h) is a read only register.

4.15

Extended Audio Status/Control Register (Index 2Ah)

VRA

Enable Variable Rate Audio. When ‘set’, the VRA bit allows access to the PCM Front DAC Rate

Register (Index 2Ch) and the PCM L/R ADC Rate Register (Index 32h). The bit must be ‘set’ in

order to use variable PCM playback or capture rates. The VRA bit also serves as a powerdown

for the DAC and ADC SRC blocks. Clearing VRA will reset the PCM Front DAC Rate Register

(Index 2Ch) and the PCM L/R ADC Rate Register (Index 32h) to their default values. The SRC

data path is flushed and the Slot Request bits for the currently active DAC slots will be fixed at

‘0’.

Default

0000h

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

ID1

ID0

0

0

0

0

AMAP

0

0

0

0

0

0

0

0

VRA

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

VRA

28

DS319PP6

CS4299