Fpga overview, 1 fpga architecture, 2 internal sub-clock routing – Cirrus Logic CDB4270 User Manual

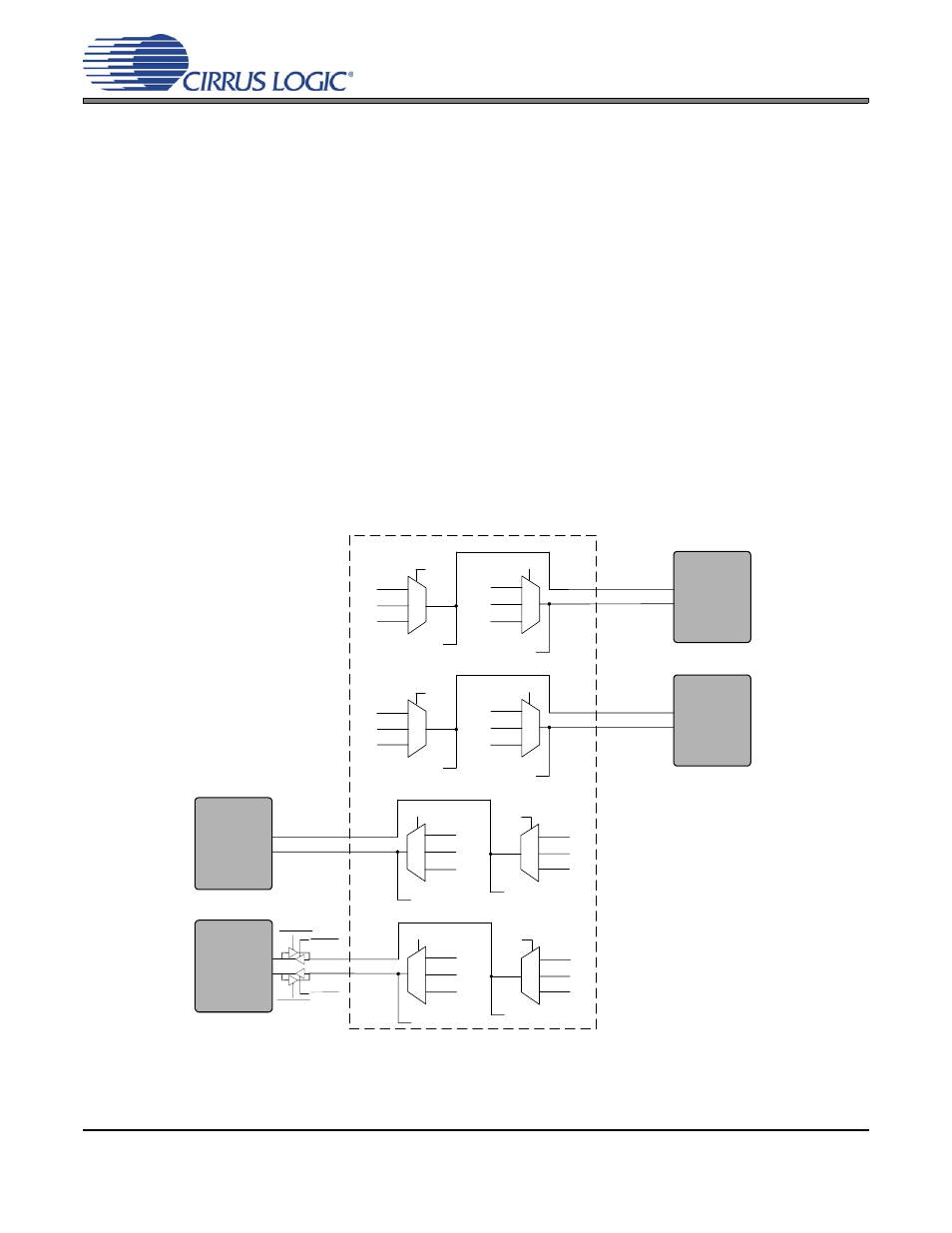

Page 9: Figure 3. internal sub-clock routing, 1 fpga architecture 2.2 internal sub-clock routing, Figure 3.internal sub-clock routing, For a comp, Cdb4270

DS686DB3

9

CDB4270

2. FPGA OVERVIEW

The FPGA (U11) controls all digital signal routing between the CS4270, CS8406, CS8416 and the DSP I/O Header.

The device also generates all of the clock/data driver output enables and S/PDIF device mode controls. The FPGA

internal registers can be configured either via the I²C (Software Mode) or via external dip switches (Hardware Mode).

When using the CS4270 in Hardware Mode, the FPGA decodes some of these dip-switch settings and generates

the CS4270 control signals. In addition, the FPGA distributes resets from the micro for all of the devices on the

board.

2.1

FPGA Architecture

through

show the internal architecture of the FPGA.

shows the MCLK routing to/from

the FPGA and the other devices on the board. The FPGA has an I²C interface and internal registers for soft-

ware control and can also read external dip-switch settings for hardware control. Refer to the

section of this document for a description of the FPGA registers.

2.2

Internal Sub-Clock Routing

shows the internal sub-clock (SCLK, LRCK) routing topology between the CS4270, CS8416,

CS8406 and DSP Header. Refer to the

section of this document for a

description of the sub-clock routing register settings.

.

CS4270

LRCK

SCLK

CS8406

LRCK

SCLK

CS8416-FPGA-SCLK

FPGA-CS8406-SCLK

FPGA-DUT-SCLK

FPGA-CS8406-LRCK

FPGA-DUT-LRCK

HDR-SCLK

HDR-LRCK

SUB_CK[1:0]

CS8416-FPGA-LRCK

SUB_CK[1:0]

FPGA-DUT-SCLK

FPGA-CS8406-SCLK

HDR-SCLK

FPGA-CS8406-LRCK

HDR-LRCK

CS8416-FPGA-SCLK

CS8416-FPGA- LRCK

SUB_CK[1:0]

FPGA-DUT-LRCK

SUB_CK[1:0]

CS8416-FPGA-SCLK

FPGA-CS8406-SCLK

HDR-SCLK

FPGA-CS8406-LRCK

HDR-LRCK

FPGA-DUT-SCLK

FPGA- DUT-LRCK

SUB_CK[1:0]

CS8416-FPGA-LRCK

SUB_CK[1:0]

CS8416-FPGA-SCLK

FPGA-DUT-SCLK

HDR-SCLK

FPGA-DUT-LRCK

HDR-LRCK

FPGA-CS8406-SCLK

FPGA-CS8406- LRCK

SUB_CK[1:0]

CS8416-FPGA-LRCK

SUB_CK[1:0]

DSP Header

LRCK

SCLK

SUBCLK.TO.HDR

SUBCLK.FROM.HDR

CS8416

LRCK

SCLK

SUBCLK.TO.HDR

SUBCLK.FROM.HDR

FPGA

Figure 3. Internal Sub-Clock Routing