Cirrus Logic CDB4270 User Manual

Cdb4270, Evaluation board for cs4270, Cs4270

Copyright

© Cirrus Logic, Inc. 2006

(All Rights Reserved)

Evaluation Board for CS4270

Features

Single-Ended Analog Audio Inputs and Outputs

CS8416 S/PDIF Digital Audio Receiver

Header for External Configuration of CS4270

Header for External DSP Serial Audio I/O

3.3V Logic Interfaces

Pre-Defined Software Scripts

Demonstrates Recommended Layout

Windows

®

-Compatible GUI Interface for Board

Configuration and Control

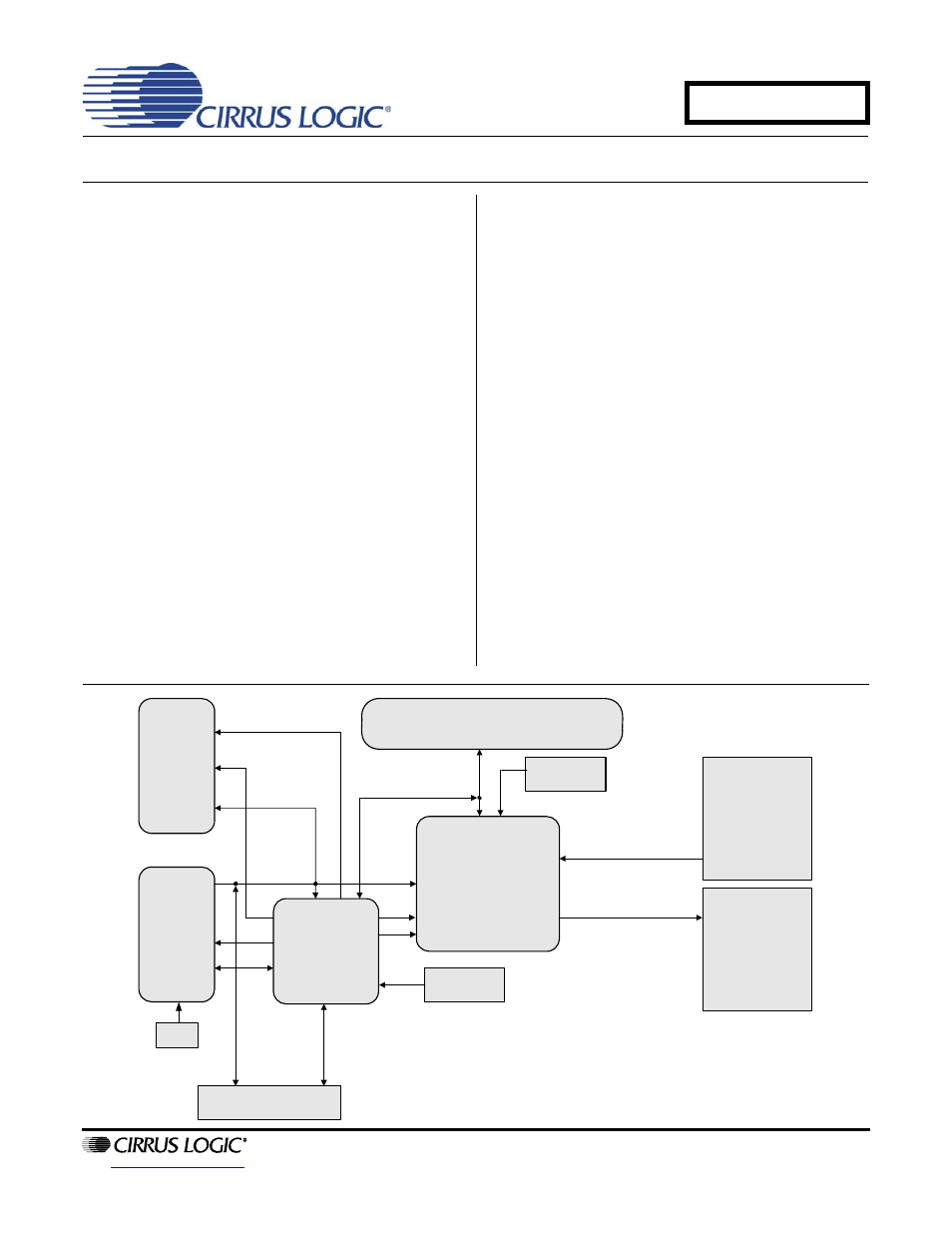

Description

Using the CDB4270 is an excellent way to evaluate the

CS4270 CODEC. Other equipment required includes

analog/digital audio sources/analyzer, a 5V power sup-

ply and a Windows-compatible

PC for the GUI.

System timing for the I²S, Left-Justified or Right-Justi-

fied audio data formats can be provided by the CS4270,

by the CS8416, or by a device connected to the on-

board DSP I/O header. The evaluation board may also

be configured to accept external timing and data signals

for operation in a user application during system

development.

RCA jacks are provided for the analog audio inputs and

outputs. Digital S/PDIF transmit or receive data I/O is

available via either RCA jacks or optical connectors.

The Windows GUI software provided allows for easy

configuration of the CDB4270. The GUI software com-

municates with the board via USB or serial port

connections to configure the CS4270 registers.

ORDERING INFORMATION

CDB4270

Evaluation Board

CDB4270

SEPTEMBER '06

DS686DB3

CS4270

CS8416

S/PDIF

Input

Single-Ended

Output

Single-Ended Input

Serial/USB Control Port

FPGA

CS8406

S/PDIF

Output

DSP HEADER

Osc.

ANALOG INPUT

ANALOG OUTPUT

Clocks

/Data

Hardware

Setup

MCLK BUS

A

D

C

/D

A

C

C

lo

cks

& D

a

ta

ADC/DAC

Clocks/

Data

C

lo

cks/

D

a

ta

I

2

C/SPI Header

HW Setup

Switches

Hardware

Setup

Hardware

Setup

Document Outline

- 1. System Overview

- 2. FPGA Overview

- 3. Software Mode

- 4. Hardware Mode

- 5. FPGA GUI Register Description

- 5.1 FPGA REGISTER QUICK REFERENCE

- 5.2.1 Revision Number Bits (Bits 7:0)

- 5.3.1 SDOUT Routing to Header (Bits 7:6)

- 5.3.2 MCLK Source (Bit 4)

- 5.3.3 SDOUT Routing to DUT (Bits 3:2)

- 5.3.4 Subclock Routing (Bits 1:0)

- 5.4.1 CS8406 OMCLK Divider Control (Bits 7:6)

- 5.4.2 CS8406 Master/Slave Select (Bit 4)

- 5.4.3 CS8406 SDIN Format Select (Bit 3)

- 5.4.4 CS8406 SDIN Source (Bits 1:0)

- 5.5.1 CS8416 RMCLK Divider Control (Bit 6)

- 5.5.2 CS8416 Master/Slave Select (Bit 4)

- 5.5.3 CS8416 SDOUT Format Select (Bit 3)

- 5.1 FPGA REGISTER QUICK REFERENCE

- 6. CDB4270 Hardware Mode Settings

- 7. CDB Connectors, Switches, Indicators and Jumpers

- 8. ADC Performance Plots

- Figure 11. FFT (-1 dB 48 kHz)

- Figure 12. FFT (-60 dB, 48 kHz)

- Figure 13. FFT (48 kHz, No Input)

- Figure 14. 48 kHz, THD+N vs. Input Freq

- Figure 15. 48 kHz, THD+N vs. Level

- Figure 16. 48 kHz, Fade-to-Noise Linearity

- Figure 17. 48 kHz, Frequency Response

- Figure 18. 48 kHz, Crosstalk

- Figure 19. FFT (-1 dB 96 kHz)

- Figure 20. FFT (-60 dB, 96 kHz)

- Figure 21. FFT (96 kHz, No Input)

- Figure 22. 96 kHz, THD+N vs. Input Freq

- Figure 23. 96 kHz, THD+N vs. Level

- Figure 24. 96 kHz, Fade-to-Noise Linearity

- Figure 25. 96 kHz, Frequency Response

- Figure 26. 96 kHz, Crosstalk

- Figure 27. FFT (-1 dB 192 kHz)

- Figure 28. FFT (192 kHz, -60 dB)

- Figure 29. FFT (192 kHz, No Input)

- Figure 30. 192 kHz, THD+N vs. Input Freq

- Figure 31. 192 kHz, THD+N vs. Level

- Figure 32. 192 kHz, Fade-to-Noise Linearity

- Figure 33. 192 kHz, Frequency Response

- Figure 34. 192 kHz, Crosstalk

- 9. DAC Performance Plots

- Figure 35. FFT (48 kHz, 0 dB)

- Figure 36. FFT (48 kHz, -60 dB)

- Figure 37. FFT (48 kHz, No Input)

- Figure 38. FFT (48 kHz Out-of-Band, No Input)

- Figure 39. 48 kHz, THD+N vs. Input Freq

- Figure 40. 48 kHz, THD+N vs. Level

- Figure 41. 48 kHz, Fade-to-Noise Linearity

- Figure 42. 48 kHz, Frequency Response

- Figure 43. 48 kHz, Crosstalk

- Figure 44. 48 kHz, Impulse Response

- Figure 45. FFT (96 kHz, 0 dB)

- Figure 46. FFT (96 kHz, -60 dB)

- Figure 47. FFT (96 kHz, No Input)

- Figure 48. FFT (96 kHz Out-of-Band, No Input)

- Figure 49. 96 kHz, THD+N vs. Input Freq

- Figure 50. 96 kHz, THD+N vs. Level

- Figure 51. 96 kHz, Fade-to-Noise Linearity

- Figure 52. 96 kHz, Frequency Response

- Figure 53. 96 kHz, Crosstalk

- Figure 54. 96 kHz, Impulse Response

- Figure 55. FFT (192 kHz, 0 dB)

- Figure 56. FFT (192 kHz, -60 dB)

- Figure 57. FFT (192 kHz, No Input)

- Figure 58. FFT (192 kHz Out-of-Band, No Input)

- Figure 59. 192 kHz, THD+N vs. Input Freq

- Figure 60. 192 kHz, THD+N vs. Level

- Figure 61. 192 kHz, Fade-to-Noise Linearity

- Figure 62. 192 kHz, Frequency Response

- Figure 63. 192 kHz, Crosstalk

- Figure 64. 192 kHz, Impulse Response

- 10. CDB Block Diagram

- 11. CDB Schematics

- 12. CDB Layout

- 13. Changes Made to Rev. B Board

- 14. Revision History