6 chipset, Dram frequency [auto, Configure dram timing by spd [enabled – Asus Pedestal Server TS100-E4/PI2 User Manual

Page 86: Dram cas# latency [5 clocks, Dram ras# precharge [4 clocks, Dram ras# to cas# delay [4 clocks

4-24

Chapter 4: BIOS setup

DRAM Frequency [Auto]

Allows you to set the DDR operating frequency.

Configuration options: [Auto] [533 MHz] [667 MHz]

Configure DRAM Timing by SPD [Enabled]

When this item is enabled, the DRAM timing parameters are set according

to the DRAM SPD (Serial Presence Detect). When disabled, you can manu-

ally set the DRAM timing parameters through the DRAM sub-items. The fol-

lowing sub‑items appear when this item is disabled. Configuration options:

[Disabled] [Enabled]

DRAM CAS# Latency [5 Clocks]

Controls the latency between the SDRAM read command and the time

the data actually becomes available. Configuration options: [5 Clocks]

[4 Clocks] [3 Clocks] [6 Clocks]

DRAM RAS# Precharge [4 Clocks]

Controls idle clocks after issuing a precharge command to the DDR

SDRAM. Configuration options: [2 Clocks] [3 Clocks] [4 Clocks] [5

Clocks]

DRAM RAS# to CAS# Delay [4 Clocks]

Controls the latency between the DDR SDRAM active command and

the read/write command. Configuration options: [2 Clocks]

[3 Clocks] [4 Clocks] [5 Clocks]

DRAM RAS# Activate to Precharge Delay [15 DRAM Clocks]

Configuration options: [1 Clocks] [2 Clocks] ~ [15 Clocks]

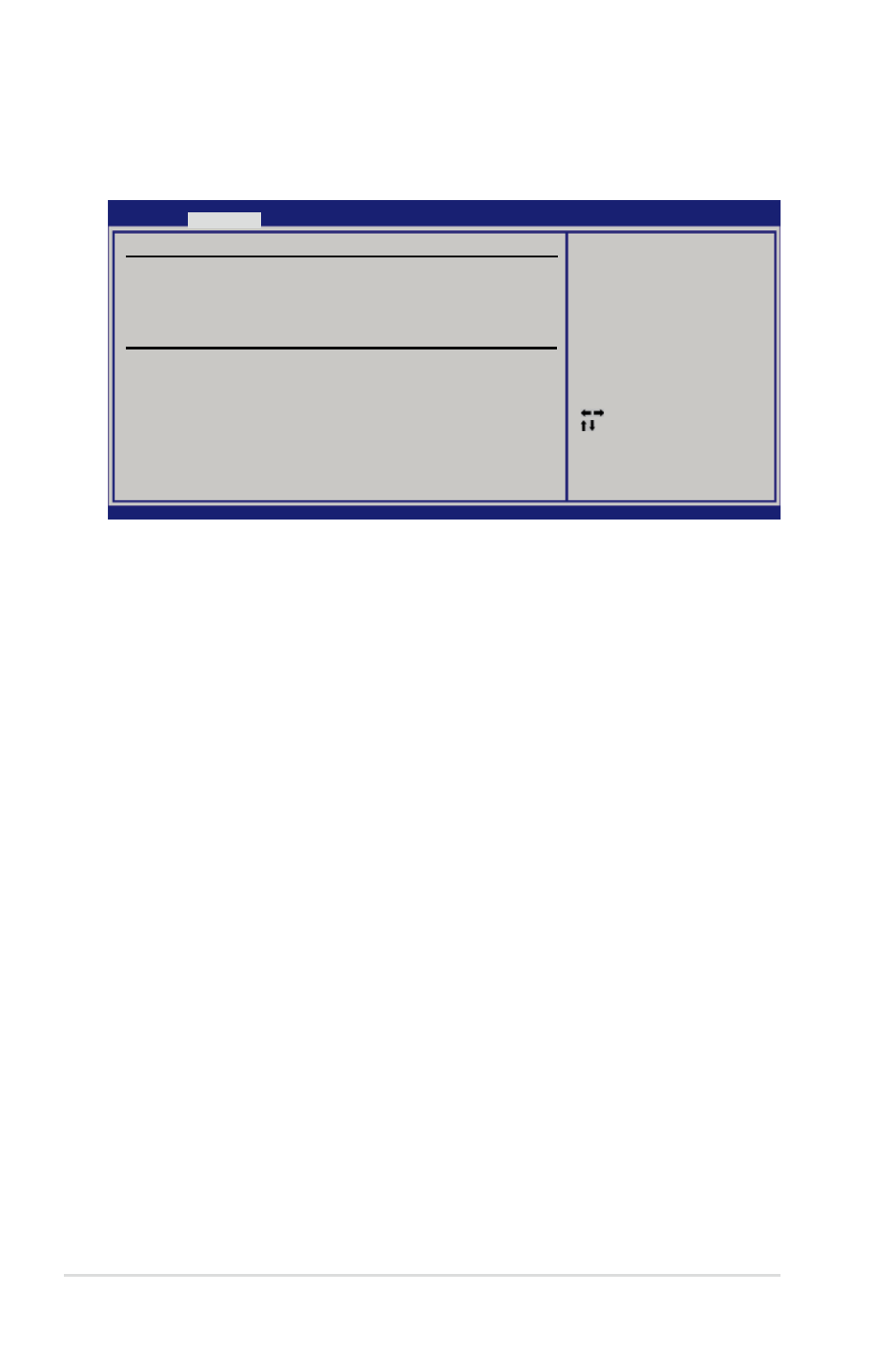

4.4.6 Chipset

The Chipset Configuration menu allows you to change the advanced chipset

settings. Select an item then press

Select Screen

Select Item

+- Change Option

F1 General Help

F10 Save and Exit

ESC Exit

v02.58 (C)Copyright 1985-2004, American Megatrends, Inc.

BIOS SETUP UTILITY

Advanced

Manual DRAM Frequency

Setting or Auto by SPD

Advanced Chipset Settings

DRAM Frequency

[Auto]

Configure DRAM Timing by SPD

[Enabled]

Onboard LAN Boot ROM

[Enabled]

PEG Port Configuration

PEG Port

[Enabled]

PEG Port VC1 Map

[TC7]

PEG Force x1

[Disabled]

Memory Remap Feature

[Enabled]