AMD Am79C930 User Manual

Page 60

AMD

P R E L I M I N A R Y

60

Am79C930

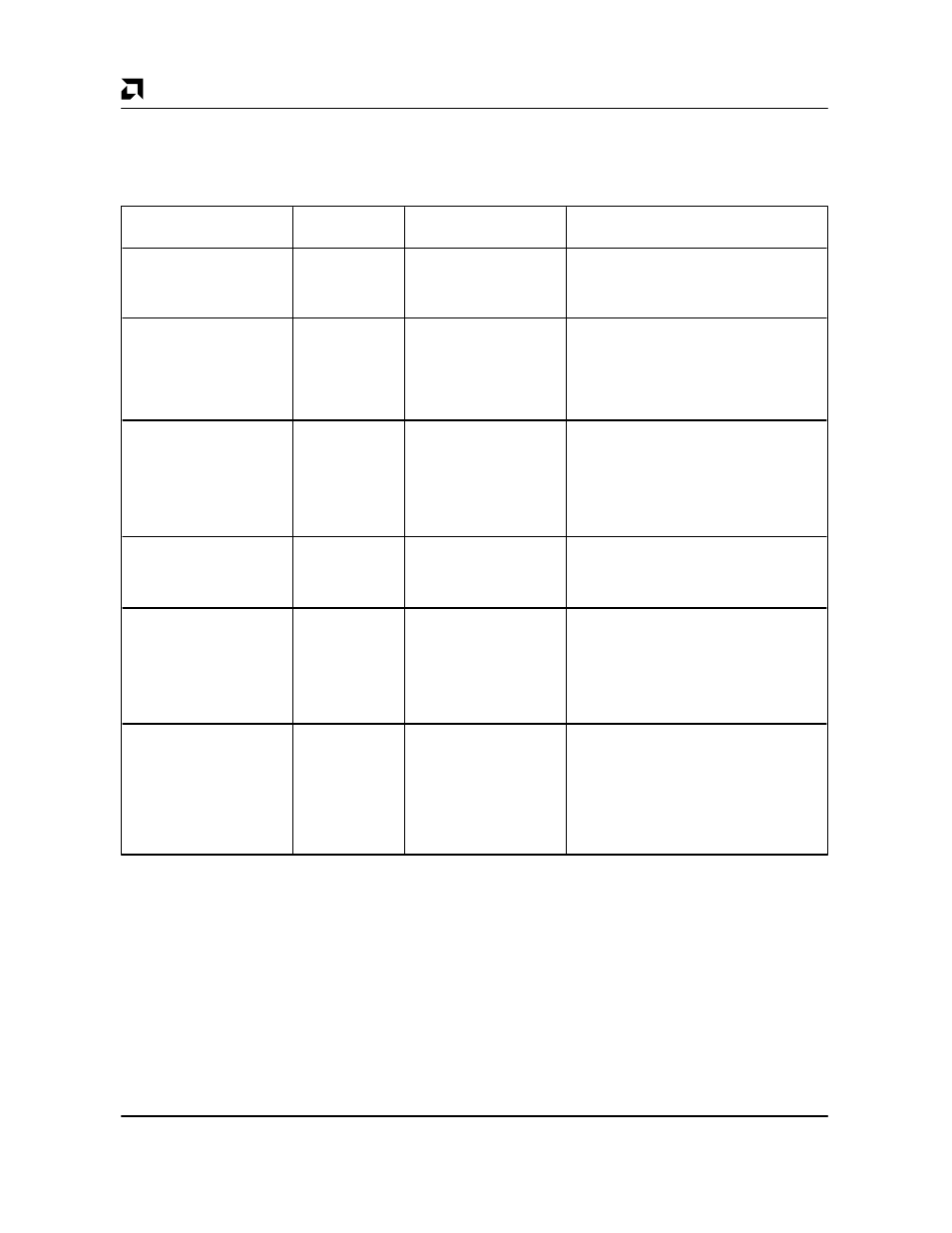

Some of the Am79C930 device’s PCMCIA Common

Memory locations have predefined uses and, therefore,

are not freely available to the device driver. The

following table indicates restricted space

within PCMCIA Common Memory map of the

Am79C930 device:

Am79C930 Device PCMCIA Mode Common Memory Restricted Space

PCMCIA Address

Size of

Physical Memory and

in Common Memory

SIR1[5:3]

Restricted Space

Description of Reserved Use

0000h – 03FFh

000

1 Kbytes

SRAM Memory 0 0000h – 0 03FFh

This space is reserved for the interrupt

vector table of the embedded 80188

core.

0400h – 041Fh

000

32 bytes

SRAM Memory 0 0400h – 0 041Fh

This SRAM space is inaccessible to

the 80188 embedded core, since the

80188 core maps the 32 TIR registers

of the TAI into this portion of 80188

memory space.

0420h – 043Fh

000

32 bytes

SRAM Memory 0 0420h – 0 042Fh

This SRAM space is inaccessible to

the 80188 embedded core, since the

80188 core maps the MIR registers of

the BIU (PIR, PDLC and PUCT) and

XCE space into this portion of 80188

memory space.

0440h – 047Fh

000

64 bytes

SRAM Memory 0 0440h – 0 047Fh

This SRAM space is reserved for future

use and may be decoded for non-

SRAM purposes in the future.

7C00h – 7FEFh

111

1K–16 bytes

Flash Memory 1 FC00h – 1 FFEFh

These bytes of the Flash memory also

map into PCMCIA Attribute Memory

space 0000h – 03FFh, which is used

for storing the CIS for the device.

Therefore, this space cannot be used

for non-CIS purposes.

7FF0h – 7FFFh

111

16 bytes

Flash Memory 1 FFF0h – 1 FFFFh

These 16 bytes of Flash memory

space are reserved because they are

the location of the embedded 80188

core’s instruction pointer following a

Am79C930 device reset operation.

These 16 bytes must contain the first

80188 instructions.