Atec Anritsu-MP1763C-64C-64D User Manual

Page 7

7

•

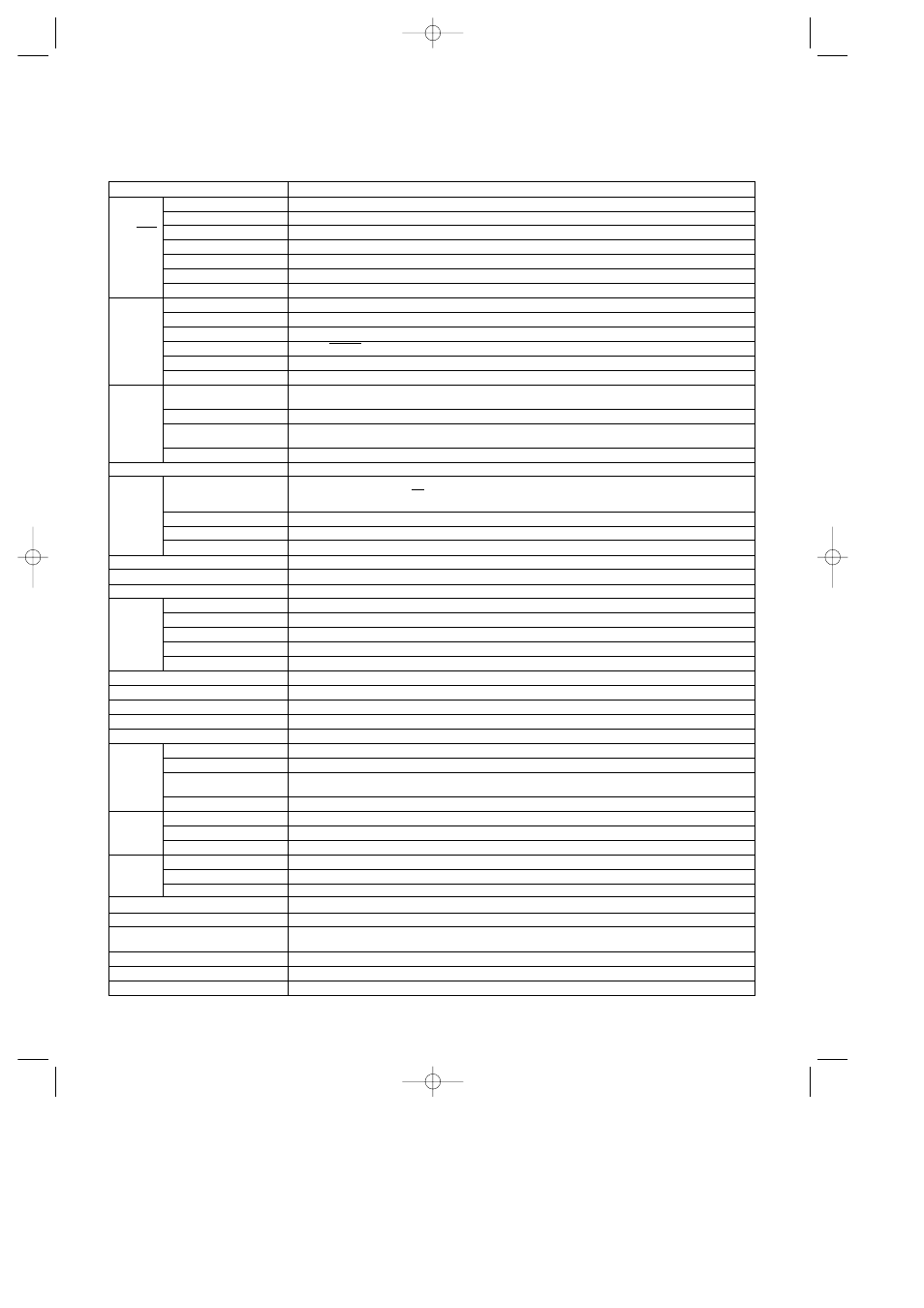

MP1764C/MP1764D Error Detector

Operation frequency

0.05 to 12.5 GHz

Input waveform

NRZ

Input amplitude

0.25 to 2.0 Vp-p

Threshold voltage variable range

–3.000 to +1.875 Vp-p (1 mV steps)

Phase margin

≥

70 ps (typical value at 10 Gbit/s, PRBS 2

23

– 1, at single ended input amplitude of 1 Vp-p)

Input sensitivity

50 mVp-p (typical value at 10 Gbit/s and PRBS 2

23

– 1)

Termination

Connected to GND or –2 V via a 50

Ω

termination

Connector

APC-3.5

Input waveform

Rectangular wave (<0.5 GHz), rectangular or sine wave (

≥

0.5 GHz), duty factor: 50%

Input voltage

0.25 to 2.0 Vp-p

CLOCK

Input delay variable range

±500 ps (1 ps steps)

input

Polarity inversion

CLOCK/CLOCK inversion possible

Termination

Connected to GND or –2 V via a 50

Ω

termination

Connector

APC-3.5

Operation bit rate

62.5 to 100 Mbit/s, 125 to 200 Mbit/s, 250 to 400 Mbit/s, 500 to 800 Mbit/s, 1,000 to 1,600 Mbit/s,

2,000 to 3,200 Mbit/s, 4,250 Mbit/s ±50 ppm, 9,900 to 11,100 Mbit/s

CLOCK selection

Internal/External

Continuous 0 s tolerance

(withstand)

72 bit min.

Regenerated CLOCK output

Output level: 1.0 ±0.25 V (AC coupling)

Auto search function

Provided

Pseudorandom binary

Pattern: 2

n

– 1 (n: 7, 9, 11, 15, 20, 23, 31)

sequence pattern (PRBS)

Mark ratio: 1/2, 1/4, 1/8, 0/8 (1/2, 3/4, 7/8, 8/8 are possible with logic inversion.)

Receive

Number of AND bit shift at mark ratio setting: 1, 3 bits (selectable by using DIP switch on rear panel)

pattern

DATA pattern

DATA length: 2 to 8388608 bits

Alternate pattern

A/B pattern word length: 128 to 4194304 bits (128 bits steps), Number of loops: Controlled using external signal

Zero substitution pattern

Zero bit length: 1 to (pattern length –1) bits, Pattern length: 2

n

(n: 7, 9, 11, 15)

Synchronous mode

Normal, frame, quick

Synchronous threshold

Preset value or 10

–n

(n: 2, 3, 4, 5, 6, 7, 8)

Error detection mode

Omission insertion, total (selectable with DIP switch on rear panel)

Error rate

0.0000 x 10

–16

to 1.0000 x 10

–0

Number of errors

0 to 9.9999 x 10

16

Measure-

Error interval (asynchronous)

0 to 9999999 (interval: 1 ms, 10 ms, 100 ms, 1 s)

ment item

Error free interval (EFI)

0.0000% to 100.0000%

CLOCK frequency

0.05 to 12.5 GHz, (resolution: 1 kHz, accuracy: 10 ppm ±1 kHz)

Eye margin measurement function

Provided

Error performance DATA calculation function

Provided

Measurement CH mask

1 to 32 ch (settable independently)

Block window

Error for any block of 32-bit segments can be measured.

Error analysis (option 01)

Pattern (256 bits in total) before and after bit in which error occurred is stored.

Error output (direct)

1/128 OR error, Output level: 0/–1 V, Connector: SMA

Error output (stretched)

Pulse width: 350 ns (typical), Output level: TTL, Connector: BNC

Auxiliary

Alarm output (CLOCK loss,

Output level: TTL

output

sync. loss)

Connector: BNC

Sync. gain output

Output level: 0/–1 V; Connector: SMA

Auxiliary

External mask input

Input level: 0/–1 V; Connector: SMA

input

Resync. input

Input level: 0/–1 V; Connector: SMA

Alternate A/B switching input

Input level: ECL; Connector: SMA

Sync. signal

Number of outputs

1 (1/32 CLOCK, fixed position pattern, or variable position pattern selectable)

output

Output level

0/–1 V

Connector

SMA

Parameter memory

Media: 3.5 inch FD (2HD, 2DD), Format: MS-DOS (Rev. 3.1)

∗

1,

Content: Pattern or other parameters

Operating temperature range

0˚ to +50˚C

Dimensions and mass

426 (W) x 221.5 (H) x 450 (D) mm,

≤

30

kg

(except Option 02, 03)

426 (W) x 266 (H) x 450 (D) mm,

≤

35

kg

(Option 02, 03)

Power

≤

300 VA

EMC

EN61326: 1997/A2: 2001 (Class A), EN61000-3-2: 2000 (Class A), EN61326: 1997/A2: 2001 (Annex A)

LVD

EN61010-1: 2001 (Pollution Degree 2)

∗

1: MS-DOS is a registered trade mark of Microsoft Corporation.

DATA/DATA

input

(MP1764D

Option 02)

CLOCK

regeneration

function

(MP1764D

Option 03)

MP1763C/1764C_E 04.6.24 3:02 PM Page 7