Atec Anritsu-MP1763C-64C-64D User Manual

Page 2

2

High-Speed/Wide Band, High Quality Waveform and

Advanced Functions

Today’s demand for transfer of large amounts of data, such as

video, over the internet, is resulting in expansion of high-speed

transmission circuits and other infrastructure. In addition to the

previously used STM-64/OC-192 (9.95328 Gbit/s) standards, we

are also seeing use of 10.709225 Gbit/s (OTU-2), which includes

FEC coding, as well as 3.125 Gbit/s x 4 and 10.3125 Gbit/s in 10

Gbit Ethernet. Furthermore, the Fibre Channel file transfer protocol

at 4.25 Gbit/s is also coming into actual use.

As these new standards are settled upon, there is an urgent need

to be able to support evaluation of devices and circuits at these

higher bit rates.

Our MP1763C Pulse Pattern Generator and MP1764C/1764D Error

Detector are a BERTS (Bit Error Rate Test Set) supporting evalua-

tion and testing of transmission equipment, high-speed devices,

optical modules, etc., at every stage from R&D through to manufac-

turing and production at speeds from 50 Mbit/s to 12.5 Gbit/s.

High-speed And Wide Band

One MP1763C/MP1764C can cover the band from STM-0/STS-1 to

10 Gbit Ethernet, STM-64/STS-192, OTU-2 and can be used with

4.25 Gbit/s Fibre Channel Systems.

Many Patterns

•

8 Mbit programmable pattern (corresponding to six frames of

STM-64/STS192)

•

PRBS patterns from 2

7

– 1 to 2

31

– 1

•

PRBS pattern with randomness and mark ratio variance for rigor-

ous testing

•

Alternating pattern

The MP1763C alternately sends normal and alarm patterns to a

device for response testing.

•

Zero substitution pattern

This feature is effective for testing the clock regeneration of a 3R

repeater.

Location Changeable Pattern Synchronization Trigger

This feature makes it simple to monitor the waveform at any point

in a long word pattern.

•

High Q factor

A high Q factor can be obtained by back to back connection (typi-

cal value at 10 Gbit/s, PRBS 2

23

– 1: 40 dB).

10 Gbit Ethernet I/O Interface Support

•

1/4 Differential Output (MP1763C-08 Option)

This outputs differential data at a rate of 1/4 of the standard output

(100 Mbit/s to 3.125 Gbit/s) as 4-bit parallel data. It can be used as

a data signal for evaluating high-speed devices such as XAUI and

SFI-4 P2 4 Lane devices used in 10 Gbit Ethernet and Fibre

Channel, and for evaluating high-speed buses and backplanes

such as PCI express.

•

Differential Input (MP1764C-02 Option)

This can be used for evaluation by inputting a high-speed differen-

tial signal used by XAUI, SFI-4P2 4Lane devices, PCI Express, etc.

•

Clock Recovery Function (MP1764C-03 Option)

The clock recovered from input data can be used as a trigger sig-

nal for error rate detection and waveform monitoring. Evaluation

does not require an external clock, and when used jointly with dif-

ferential input, high-speed differential devices can be evaluated

without an external jig.

Bit rates from 62.5 Mbit/s to 11.1 Gbit/s are supported along with

4.25 Gbit/s used by Fibre Channel.

High-quality Waveform

•

t

r

/t

f

(10% to 90%): 30 ps (typical)

•

Jitter: 10 ps

p-p

(typical)

•

Back termination for low waveform distortion

•

A pattern of isolated pulses which do not depend on mark ratios.

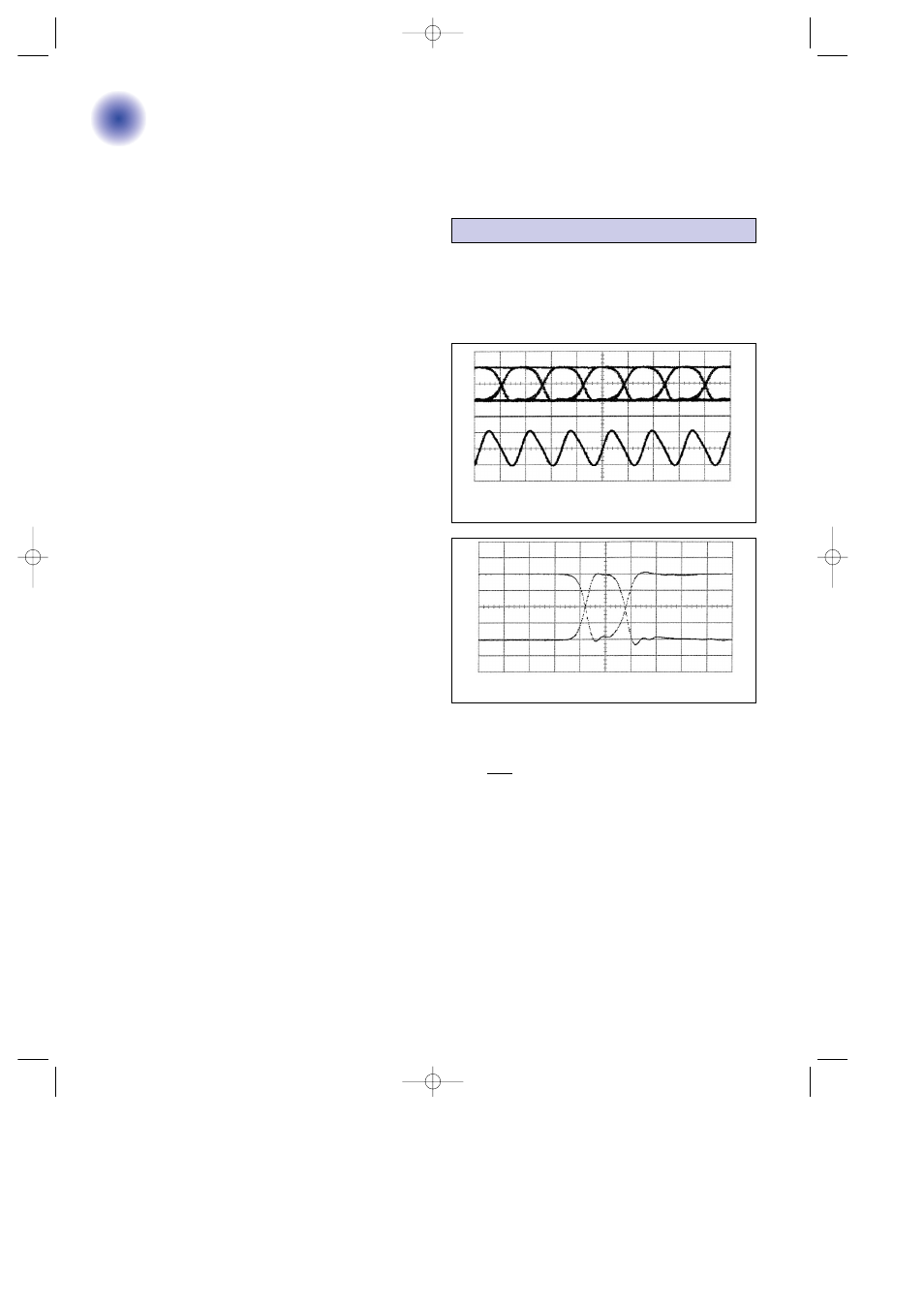

MP1763C output waveform

High Resolution Clock And Data Output

•

Output amplitude: 0.25 to 2 Vp-p (2 mV steps)

•

Output offset: –2 to +2 V (1 mV steps)

•

Delay (clock): –500 to +500 ps (1 ps steps)

•

DATA/DATA independently variable

Burst Signal Generation Using External Gate Signal

This feature is effective for optical fiber-loop testing, etc.

Parallel Output I/F (1/8, 1/4, 1/4 Differential)

•

1/8 parallel output is standard. 1/4 parallel output (Option 03) or

1/4 differential output (Option 08) can be selected exclusively.

•

It can be used as a MUX device and a data generator for WDM

transmission.

•

The 1/4 differential option provides 4-bit parallel output of differ-

ential data for the 1/4 rate standard output (100 Mbit/s to 3.125

Gbit/s). Similarly, a 1/4 rate clock can be output as a differential.

This can be used for performing detailed inspection of specifica-

tions and performance by use as a data signal for evaluation of

high-speed devices such as XAUI and SFI-4 P2 4 Lane devices

used in 10 Gbit Ethernet and Fibre Channel, and for evaluation of

high-speed buses and backplanes such as PCI express.

Pulse Pattern Generator

H: 50 ps/div, V: 1 V/div

DATA output of 12.5 GHz (top trace)

CLOCK 1 output (bottom trace)

H: 50 ps/div, V: 0.5 V/div

Isolated pattern (superimposition of 1/64 bits and 63/64 bits)

∗

The MP1764D model ships with the MP1764C-02 (Differential input) and

MP1764C-03 (Clock recovery) options installed.

MP1763C/1764C_E 04.6.24 3:02 PM Page 2