2 chipset, Chipset -18, Chapter 3 – Asus M4N98TD EVO User Manual

Page 74: Northbridge chipset configuration, Dram controller configuration, Channel interleaving [xor of address bit, Memclk tristate c3/atlvid [disabled, Dct unganged mode [always, Power down enable [disabled

3-18

Chapter 3: BIOS setup

Chapter 3

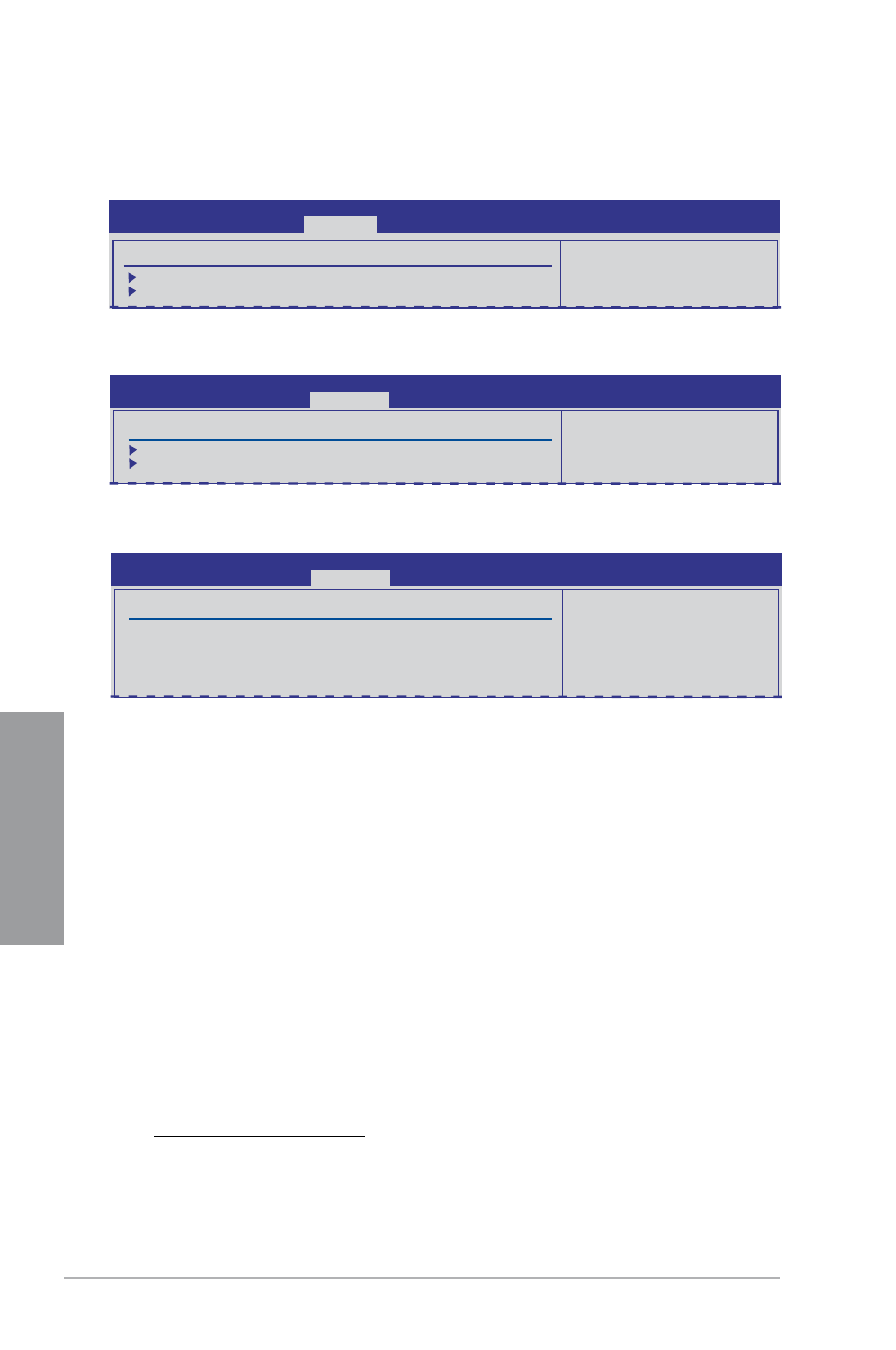

NorthBridge Chipset Configuration

BIOS SETUP UTILITY

Advanced

NorthBridge Chipset Configuration

DRAM Controller Configuration

ECC Configuration

DRAM Controller Configuration

BIOS SETUP UTILITY

Advanced

DRAM Controller Configuration

Channel Interleaving

[XOR of Address bit]

MemClk Tristate C3/ATLVID

[Disabled]

Memory Hole Remapping

[Enabled]

DCT Unganged Mode

[Always]

Power Down Enable

[Disabled]

Channel Interleaving [XOR of Address bit]

Configuration options: [Disabled] [Address bits 6] [Address bits 12]

[XOR of Address bits [20:16, 6]] [XOR of Address bits [20:16, 9]]

MemClk Tristate C3/ATLVID [Disabled]

Configuration options: [Disabled] [Enabled]

Memory Hole Remapping [Enabled]

Configuration options: [Disabled] [Enabled]

DCT Unganged Mode [Always]

Configuration options: [Auto] [Always]

Power Down Enable [Disabled]

Enables or disables the DDR power down mode.

Configuration options: [Disabled] [Enabled]

Power Down Mode [Channel]

This item appears only when you enable the previous item and allows you to set the

DDR power down mode. Configuration options: [Channel] [Chip Select]

Enable Channel Memory

Interleaving

3.6.2

Chipset

The Chipset menu allows you to change the advanced chipset settings. Select an item then

press

Options for NB

Advanced Chipset Settingsz

NorthBridge Configuration

SouthBridge Configuration

BIOS SETUP UTILITY

Advanced