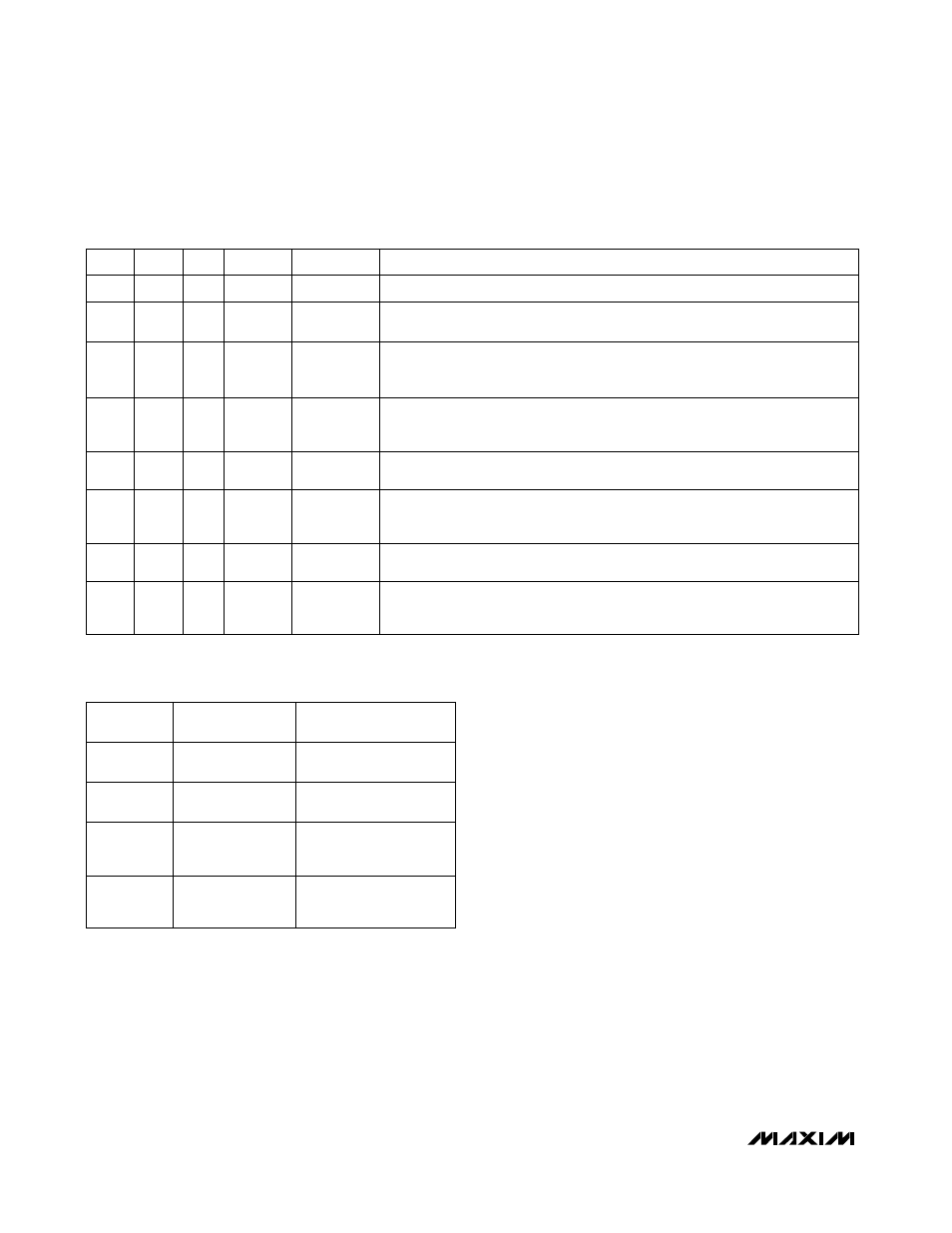

Table 4. operating mode truth table, Table 5. frequency selection guidelines – Rainbow Electronics MAX1712 User Manual

Page 16

MAX1710/MAX1711/MAX1712

High-Speed, Digitally Adjusted

Step-Down Controllers for Notebook CPUs

16

______________________________________________________________________________________

pullups on each input in order to eliminate external resis-

tors.

When changing MAX1710 DAC codes while powered

up, the over/undervoltage protection features can be

activated if the code is changed more than 1LSB at a

time. For applications needing the capability of changing

DAC codes “on-the-fly,” use the MAX1711/MAX1712.

POR, UVLO, and Soft-Start

Power-on reset (POR) occurs when V

CC

rises above

approximately 2V, resetting the fault latch and soft-start

counter, and preparing the PWM for operation. V

CC

undervoltage lockout (UVLO) circuitry inhibits switching

and forces the DL gate driver high (in order to enforce

output overvoltage protection) until V

CC

rises above

4.2V, whereupon an internal digital soft-start timer begins

to ramp up the maximum allowed current limit. The ramp

occurs in five steps: 20%, 40%, 60%, 80%, and 100%,

with 100% current available after 1.7ms ±50%.

A continuously adjustable, analog soft-start function can

be realized by adding a capacitor in parallel with R

LIM

at

ILIM. This soft-start method requires a minimum interval

between power-down and power-up to allow R

LIM

to dis-

charge the capacitor.

Power-Good Output (PGOOD)

The output (FB) is continuously monitored for undervolt-

age by the PGOOD comparator, except in shutdown or

standby mode. The -5% undervoltage trip threshold is

measured with respect to the nominal unloaded output

voltage, as set by the DAC. If the DAC code increases in

steps greater than 1LSB, it is likely that PGOOD will

momentarily go low. In shutdown and standby modes,

PGOOD is actively held low. The PGOOD output is a true

SHDN SKIP

OVP

DL

MODE

COMMENTS

1

X

0

X

0

High

Shutdown1

Low-power shutdown state. DL is forced to V

DD

, enforcing OVP. I

CC

< 1µA typ.

X

Low

0

X

1

Low

Shutdown2

Low-power shutdown state. DL is forced to GND, disabling OVP. I

CC

< 1µA typ.

Exiting shutdown triggers a soft-start cycle.

Shutdown3

(MAX1711/

MAX1712)

DAC code = X1111 (MAX1711), DAC code = 11111 (MAX1712) (Table 2). DL is

forced to PGND, DH is forced to LX. The MAX1711/MAX1712 eventually goes

into UVP fault mode as the load current discharges the output.

1

Below

GND

X

Switching

No fault

Test mode with OVP, UVP, and thermal faults disabled and latches cleared.

Otherwise normal operation, with automatic PWM/PFM switchover for pulse

skipping at light loads (Figure 6).

1

X

1

Switching

No OVP

OVP faults disabled and OVP latch cleared. Otherwise normal operation,

with SKIP controlling PWM/PFM switchover.

1

V

CC

X

Switching

Run (PWM),

Low Noise

Low-noise operation with no automatic switchover. Fixed-frequency PWM action

is forced regardless of load. Inductor current reverses at light load levels.

I

CC

draw = 750µA typ. I

DD

draw = 15mA typ.

1

GND

X

Switching

Run

(PFM/PWM)

Normal operation with automatic PWM/PFM switchover for pulse skipping at light

loads. I

CC

= 600µA typ. I

DD

draw = load dependent.

1

X

X

High

Fault

Fault latch has been set by OVP, output UVLO, or thermal shutdown. Device will

remain in FAULT mode until V

CC

power is cycled, SKIP is forced below ground,

or SHDN is toggled.

Table 4. Operating Mode Truth Table

Good operating point for

compound buck designs

or desktop circuits.

+5V-input notebook

CPU core

550

400

3-cell Li+ notebook

CPU core

Useful in 4-cell systems

for lighter loads than the

CPU or where size is key.

Considered mainstream

by current standards.

4-cell Li+ notebook

CPU core

300

Table 5. Frequency Selection Guidelines

FREQUENCY

(kHz)

TYPICAL

APPLICATION

COMMENT

200

4-cell Li+ notebook

CPU core

Use for absolute best

efficiency.