Rainbow Electronics MAX1314 User Manual

Page 23

MAX1304–MAX1306/MAX1308–MAX1310/MAX1312–MAX1314

8-/4-/2-Channel, 12-Bit, Simultaneous-Sampling ADCs

with ±10V, ±5V, and 0 to +5V Analog Input Ranges

______________________________________________________________________________________

23

Reading a Conversion Result

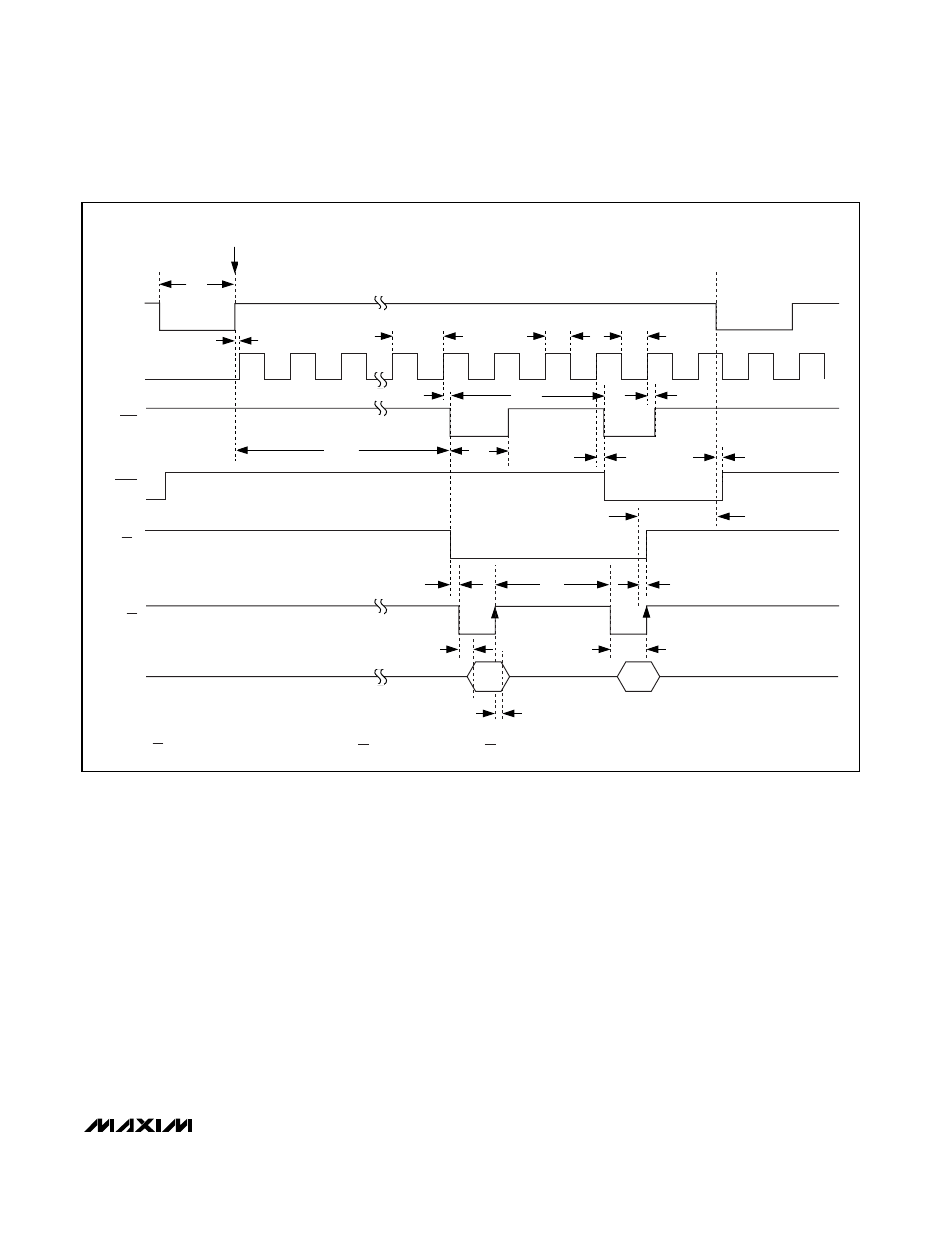

Reading During a Conversion

Figures 7 and 8 show the interface signals to initiate a

read operation during a conversion cycle. These figures

show two channels selected for conversion. If more

channels are selected, the results are available succes-

sively at every EOC falling edge. CS can be low at all

times, low during the RD cycles, or the same as RD.

After initiating a conversion by bringing CONVST high,

wait for EOC to go low. In internal clock mode, EOC

goes low within 900ns. In external clock mode, EOC

goes low on the rising edge of the 13th CLK cycle. To

read the conversion result, drive CS and RD low to

latch data to the parallel digital output bus. Bring RD

high to release the digital bus. In internal clock mode,

the next EOC falling edge occurs within 225ns. In exter-

nal clock mode, the next EOC falling edge occurs in

three CLK cycles. When the last result is available

EOLC goes low.

Reading After Conversion

Figure 9 shows the interface signals for a read operation

after a conversion with all eight channels enabled. At

the falling of EOLC, driving CS and RD low places the

first conversion result onto the parallel bus. Successive

low pulses of RD place the successive conversion

results onto the bus. When the last conversion results in

the sequence are read, additional read pulses wrap the

pointer back to the first converted result.

CONVST

CLK

CH3

TRACK

HOLD

D0–D11

SAMPLE

INSTANT

t

ACQ

t

CNTC

t

CTR

t

RDH

t

RTC

t

ACC

t

RDL

t

REQ

TRACK

CH7

EOC

RD

1

2

3

12

13

14

15

16

17

18

19

1

t

CLK

t

EOCD

t

CONV

t

NEXT

t

EOC

t

EOCD

t

CLKH

t

EOLCD

t

CVEOLCD

t

QUIET

≥ 50ns

t

CLKL

EOLC

CS*

*CS CAN BE LOW AT ALL TIMES, LOW DURING THE RD CYCLES, OR THE SAME AS RD.

Figure 8. Read During Conversion—Channel 3 and Channel 7 Selected, External Clock