Rainbow Electronics MAX1207 User Manual

Page 19

MAX1207

65Msps, 12-Bit ADC

______________________________________________________________________________________

19

edge to have the lowest possible jitter. Jitter limits the

maximum SNR performance of any ADC according to

the following relationship:

where f

IN

represents the analog input frequency and t

J

is the total system clock jitter. Clock jitter is especially

critical for undersampling applications. For example,

assuming that clock jitter is the only noise source, to

obtain the specified 68.5dB of SNR with an input fre-

quency of 32.5MHz, the system must have less than

1.8ps of clock jitter.

Clock Duty-Cycle Equalizer (DCE)

The MAX1207 clock duty-cycle equalizer allows for a

wide 20% to 80% clock duty cycle when enabled (DCE

= OV

DD

or V

DD

). When disabled (DCE = GND), the

MAX1207 accepts a narrow 45% to 65% clock duty

cycle. See the Typical Operating Characteristics section

for Dynamic Performance vs. Clock Duty-Cycle plots.

The clock duty-cycle equalizer uses a delay-locked

loop to create internal timing signals that are duty-cycle

independent. Due to this delay-locked loop, the

MAX1207 requires approximately 100 clock cycles to

acquire and lock to new clock frequencies.

Disabling the clock duty-cycle equalizer reduces the

analog supply current by 1.5mA.

System Timing Requirements

Figure 5 shows the relationship between the clock, ana-

log inputs, DAV indicator, DOR indicator, and the result-

ing output data. The analog input is sampled on the

falling edge of the clock signal and the resulting data

appears at the digital outputs 8.5 clock cycles later.

The DAV indicator is synchronized with the digital out-

put and optimized for use in latching data into digital

back-end circuitry. Alternatively, digital back-end cir-

cuitry can be latched with the falling edge of the clock.

Data Valid Output (DAV)

DAV is a single-ended version of the input clock

(CLKP). The output data changes on the falling edge of

DAV, and DAV rises once the output data is valid.

The state of the duty-cycle equalizer input (DCE)

changes the waveform at DAV. With the duty-cycle

equalizer disabled (DCE low), the DAV signal is the

inverse of the signal at CLKP delayed by 6.4ns. With

the duty-cycle equalizer enabled (DCE high), the DAV

signal has a fixed pulse width that is independent of

CLKP. In either case, with DCE high or low, output data

at D0–D11 and DOR are valid from 8.5ns before the ris-

ing edge of DAV to 6.3ns after the rising edge of DAV,

and the rising edge of DAV is synchronized to have a

6.4ns delay from the falling edge of CLKP.

DAV is high impedance when the MAX1207 is in

power-down (PD = high). DAV is capable of sinking

and sourcing 600µA and has three times the drive

strength of D0–D11 and DOR. DAV is typically used to

latch the MAX1207 output data into an external back-

end digital circuit.

Keep the capacitive load on DAV as low as possible

(<25pF) to avoid large digital currents feeding back into

the analog portion of the MAX1207 and degrading its

dynamic performance. An external buffer on DAV isolates

it from heavy capacitive loads. Refer to the MAX1211

evaluation kit schematic for an example of DAV driving

back-end digital circuitry through an external buffer.

Data Out-of-Range Indicator (DOR)

The DOR digital output indicates when the analog input

voltage is out of range. When DOR is high, the analog

input is out of range. When DOR is low, the analog

input is within range. The valid differential input range is

from (V

REFP

- V

REFN

) to (V

REFN

- V

REFP

). Signals out-

side this valid differential range cause DOR to assert

high as shown in Table 2.

DOR is synchronized with DAV and transitions along

with output data D0–D11. There is an 8.5 clock-cycle

latency in the DOR function just as with the output data

(Figure 5).

SNR

f

t

IN

J

=

Ч

Ч Ч

Ч

20

1

2

log

π

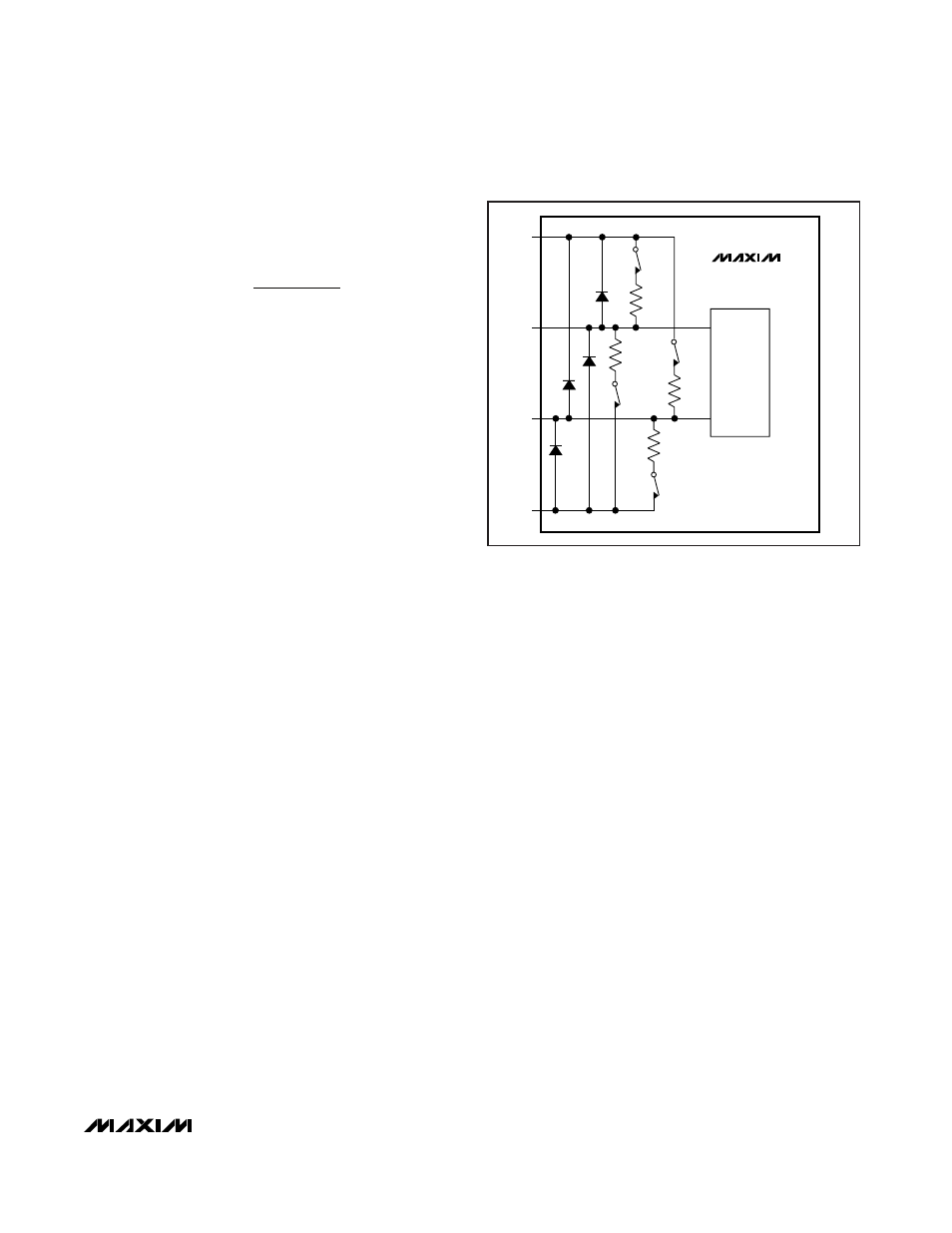

10kΩ

10kΩ

10kΩ

10kΩ

SWITCHES S

1_

AND S

2_

ARE OPEN

DURING POWER-DOWN, MAKING

CLKP AND CLKN HIGH IMPEDANCE.

SWITCHES S

2_

ARE OPEN IN

SINGLE-ENDED CLOCK MODE.

V

DD

CLKP

CLKN

GND

S

1H

S

2H

S

1L

S

2L

DUTY-

CYCLE

EQUALIZER

MAX1207

Figure 4. Simplified Clock Input Circuit